Reload/add (reload_add), Reload/add, Reload_add) – SMSC LAN9311i User Manual

Page 226: Datasheet

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08)

226

SMSC LAN9311/LAN9311i

DATASHEET

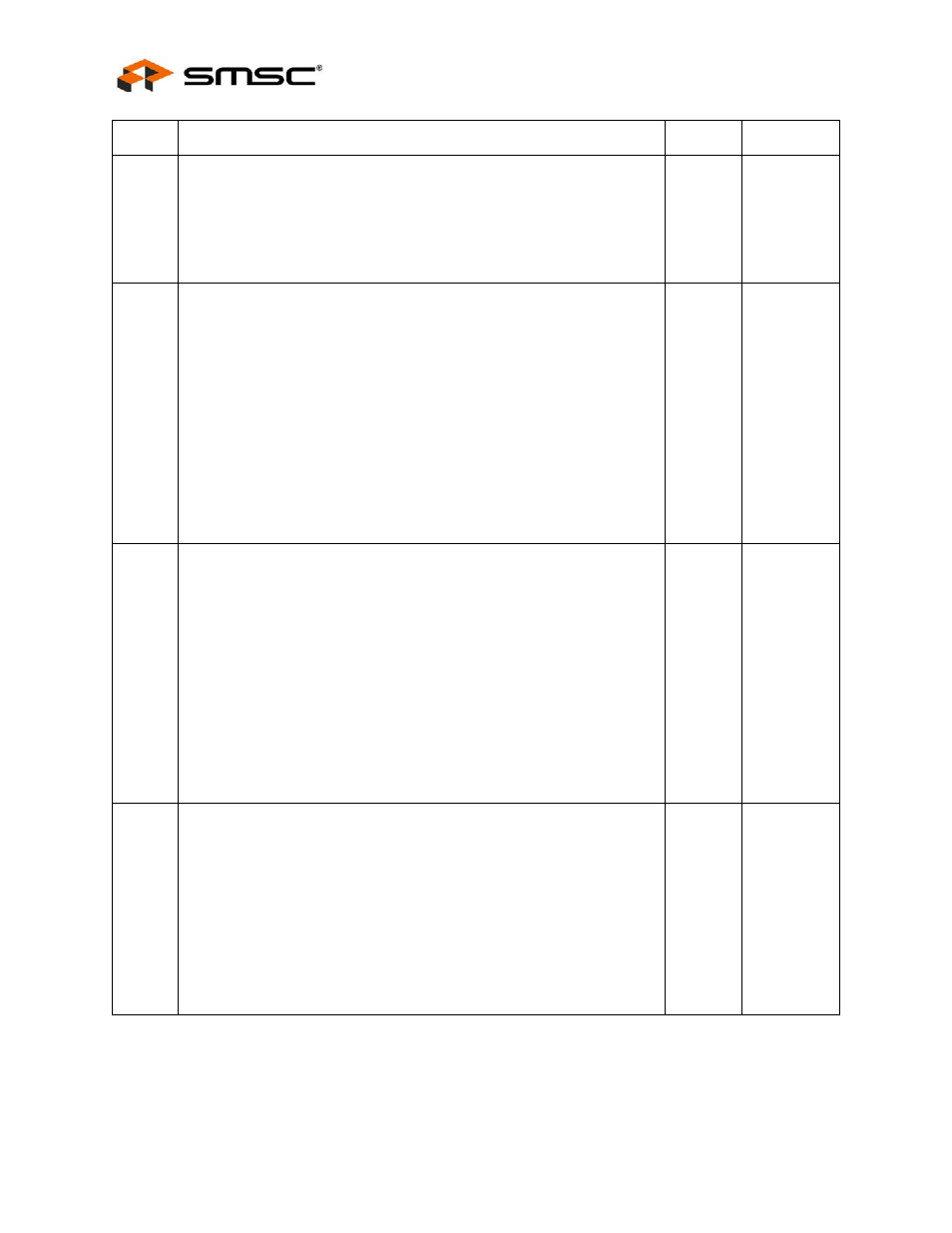

5

Lock Enable GPIO 8 (LOCK_GPIO_8)

This bit enables/disables the GPIO 8 lock. This lock prevents a 1588 capture

from overwriting the Clock value if the 1588_GPIO8 interrupt in the

Interrupt Status and Enable Register (1588_INT_STS_EN)

is already set

due to a previous capture.

0: Disables GPIO 8 Lock

1: Enables GPIO 8 Lock

R/W

1b

4:3

GPIO 9 Clock Event Mode (GPIO_EVENT_9)

These bits determine the output on GPIO 9 when a clock target compare

event occurs.

00: 100ns pulse output

01: Toggle output

10: 1588_TIMER_INT bit value in the 1588_INT_STS_EN register output

11: RESERVED

Note:

The 1588_GPIO_OE[9] bit in the

Configuration Register (GPIO_CFG)

must be set in order for the

GPIO output to be controlled by the 1588 block.

Note:

The polarity of the pulse or level is set by the

GPIO_EVENT_POL_9 bit in the

General Purpose I/O Configuration

. The GPIOBUF[9] bit still determines the

GPIO buffer type.

R/W

00b

2:1

GPIO 8 Clock Event Mode (GPIO_EVENT_8)

These bits determine the output on GPIO 8 when a clock target compare

event occurs.

00: 100ns pulse output

01: Toggle output

10: 1588_TIMER_INT bit value in the 1588_INT_STS_EN register output

11: RESERVED

Note:

The 1588_GPIO_OE[8] bit in the

Configuration Register (GPIO_CFG)

must be set in order for the

GPIO output to be controlled by the 1588 block.

Note:

The polarity of the pulse or level is set by the

GPIO_EVENT_POL_8 bit in the

General Purpose I/O Configuration

. The GPIOBUF[8] bit still determines the

GPIO buffer type.

R/W

00b

0

Reload/Add (RELOAD_ADD)

This bit determines the course of action when a clock target compare event

occurs. When set, the

1588 Clock Target High-DWORD Register

1588 Clock Target Low-DWORD Register

are loaded from the

Reload High-DWORD Register (1588_CLOCK_TARGET_RELOAD_HI)

1588 Clock Target Reload/Add Low-DWORD Register

(1588_CLOCK_TARGET_RELOAD_LO)

when a clock target compare event

occurs. When low, the Clock Target Low and High Registers are

incremented by the Clock Target Reload Low Register when a clock target

compare event occurs.

0: Reload upon a clock target compare event

1: Increment upon a clock target compare event

R/W

0b

BITS

DESCRIPTION

TYPE

DEFAULT