Datasheet – SMSC LAN9311i User Manual

Page 312

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08)

312

SMSC LAN9311/LAN9311i

DATASHEET

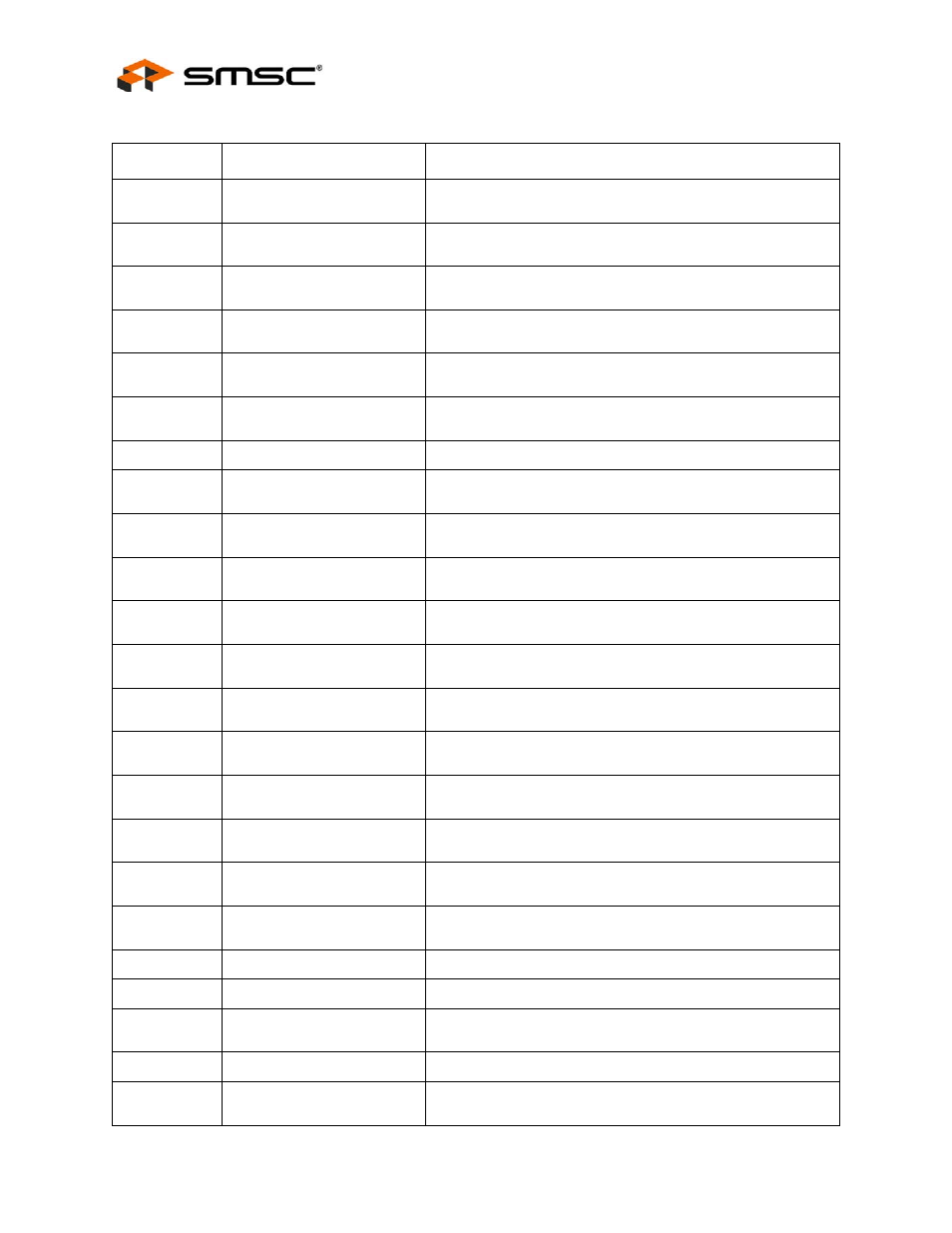

0812h

MAC_RX_65_TO_127_CNT_1

Port 1 MAC Receive 65 to 127 Byte Count Register,

0813h

MAC_RX_128_TO_255_CNT_1

Port 1 MAC Receive 128 to 255 Byte Count Register,

0814h

MAC_RX_256_TO_511_CNT_1

Port 1 MAC Receive 256 to 511 Byte Count Register,

0815h

MAC_RX_512_TO_1023_CNT_1

Port 1 MAC Receive 512 to 1023 Byte Count Register,

0816h

MAC_RX_1024_TO_MAX_CNT_1

Port 1 MAC Receive 1024 to Max Byte Count Register,

0817h

MAC_RX_OVRSZE_CNT_1

Port 1 MAC Receive Oversize Count Register,

0818h

MAC_RX_PKTOK_CNT_1

Port 1 MAC Receive OK Count Register,

0819h

MAC_RX_CRCERR_CNT_1

Port 1 MAC Receive CRC Error Count Register,

081Ah

MAC_RX_MULCST_CNT_1

Port 1 MAC Receive Multicast Count Register,

081Bh

MAC_RX_BRDCST_CNT_1

Port 1 MAC Receive Broadcast Count Register,

081Ch

MAC_RX_PAUSE_CNT_1

Port 1 MAC Receive Pause Frame Count Register,

081Dh

MAC_RX_FRAG_CNT_1

Port 1 MAC Receive Fragment Error Count Register,

081Eh

MAC_RX_JABB_CNT_1

Port 1 MAC Receive Jabber Error Count Register,

081Fh

MAC_RX_ALIGN_CNT_1

Port 1 MAC Receive Alignment Error Count Register,

0820h

MAC_RX_PKTLEN_CNT_1

Port 1 MAC Receive Packet Length Count Register,

0821h

MAC_RX_GOODPKTLEN_CNT_1

Port 1 MAC Receive Good Packet Length Count Register,

0822h

MAC_RX_SYMBL_CNT_1

Port 1 MAC Receive Symbol Error Count Register,

0823h

MAC_RX_CTLFRM_CNT_1

Port 1 MAC Receive Control Frame Count Register,

0824h-083Fh

RESERVED

Reserved for Future Use

0840h

MAC_TX_CFG_1

Port 1 MAC Transmit Configuration Register,

0841h

MAC_TX_FC_SETTINGS_1

Port 1 MAC Transmit Flow Control Settings Register,

0842h-0850h

RESERVED

Reserved for Future Use

0851h

MAC_TX_DEFER_CNT_1

Port 1 MAC Transmit Deferred Count Register,

Table 14.12 Indirectly Accessible Switch Control and Status Registers (continued)

REGISTER #

SYMBOL

REGISTER NAME