4 power management control register (pmt_ctrl), Power management control register (pmt_ctrl), Power management control register – SMSC LAN9311i User Manual

Page 264: Pmt_ctrl), Power management control, Register (pmt_ctrl), Power, Management control register (pmt_ctrl), Section 14.2.9.4, Must first be

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08)

264

SMSC LAN9311/LAN9311i

DATASHEET

14.2.9.4

Power Management Control Register (PMT_CTRL)

This read-write register controls the power management features and the PME pin of the

LAN9311/LAN9311i. The ready state of the LAN9311/LAN9311i can be determined via the Device

Ready (READY) bit of this register. Refer to

Section 4.3, "Power Management," on page 46

additional information.

Note:

This register is one of only four registers (the others are HW_CFG, BYTE_TEST, and

RESET_CTL) which can be polled while the LAN9311/LAN9311i is in the reset or not ready

state (READY bit is cleared).

Note:

Either half of this register can be read without the need to read the other half.

Offset:

084h

Size:

32 bits

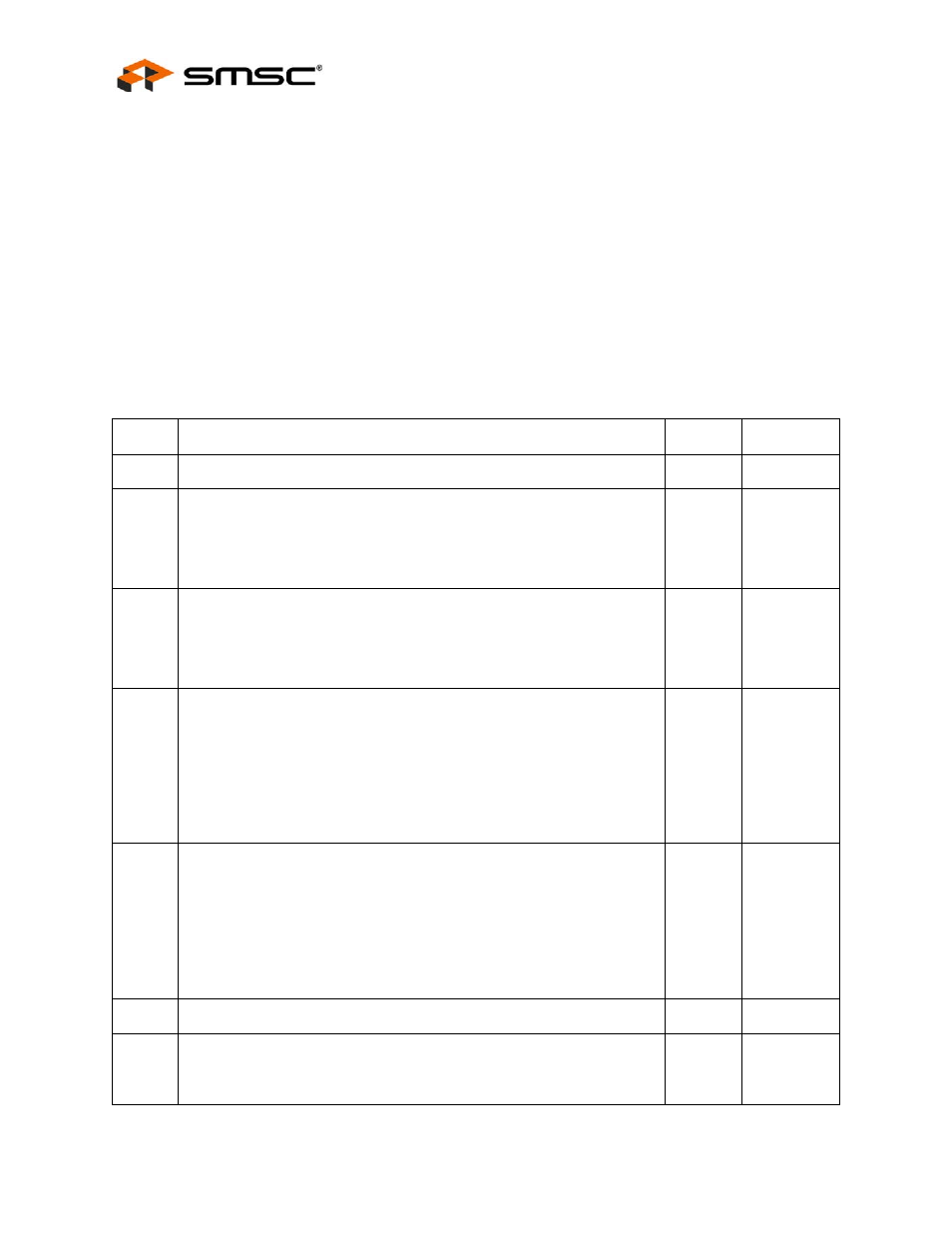

BITS

DESCRIPTION

TYPE

DEFAULT

31:18

RESERVED

RO

-

17

Energy-Detect Status Port 2 (ED_STS2)

This bit indicates an energy detect event occurred on the Port 2 PHY.

In order to clear this bit, it is required that the event in the PHY be cleared

as well. The event sources are described in

R/WC

0b

16

Energy-Detect Status Port 1 (ED_STS1)

This bit indicates an energy detect event occurred on the Port 1 PHY.

In order to clear this bit, it is required that the event in the PHY be cleared

as well. The event sources are described in

R/WC

0b

15

Energy-Detect Enable Port 2 (ED_EN2)

When set, the PME signal (if enabled via the PME_EN bit) will be asserted

in accordance with the PME_IND bit upon an energy-detect event from Port

2. When set, the PME_INT bit in the

Interrupt Status Register (INT_STS)

will

also be asserted upon an energy-detect event from Port 2, regardless of the

setting of the PME_EN bit.

Note:

The EDPWRDOWN bit of the

Port x PHY Mode Control/Status

Register (PHY_MODE_CONTROL_STATUS_x)

of the Port 2 PHY

must also be set to enable the energy detect feature.

R/W

0b

14

Energy-Detect Enable Port 1 (ED_EN1)

When set, the PME signal (if enabled via the PME_EN bit) will be asserted

in accordance with the PME_IND bit upon an energy-detect event from Port

1. When set, the PME_INT bit in the

Interrupt Status Register (INT_STS)

will

also be asserted upon an energy-detect event from Port 1, regardless of the

setting of the PME_EN bit.

Note:

The EDPWRDOWN bit in the

Port x PHY Mode Control/Status

Register (PHY_MODE_CONTROL_STATUS_x)

of the Port 1 PHY

must also be set to enable the energy detect feature.

R/W

0b

13:11

RESERVED

RO

-

10

Virtual PHY Reset (VPHY_RST)

Writing a 1 to this bit resets the Virtual PHY. When the Virtual PHY is

released from reset, this bit is automatically cleared. All writes to this bit are

ignored while this bit is high.

R/W

SC

0b