2 system control and status registers, Table 14.1 system control and status registers, System control and status registers – SMSC LAN9311i User Manual

Page 169: Section 14.2, "system, Control and status registers, Datasheet

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i

169

Revision 1.4 (08-19-08)

DATASHEET

14.2

System Control and Status Registers

The System CSR’s are directly addressable memory mapped registers with a base address offset

range of 050h to 2DCh. These registers are addressable by the Host via the Host Bus Interface (HBI).

lists the System CSR’s and their corresponding addresses in order. All system CSR’s are

reset to their default value on the assertion of a chip-level reset.

The System CSR’s can be divided into 9 sub-categories. Each of these sub-categories contains the

System CSR descriptions of the associated registers. The register descriptions are categorized as

follows:

Section 14.2.1, "Interrupts," on page 173

Section 14.2.2, "Host MAC & FIFO’s," on page 181

Section 14.2.3, "GPIO/LED," on page 193

Section 14.2.4, "EEPROM," on page 198

Section 14.2.5, "IEEE 1588," on page 202

Section 14.2.6, "Switch Fabric," on page 230

Section 14.2.7, "PHY Management Interface (PMI)," on page 244

Section 14.2.8, "Virtual PHY," on page 246

Section 14.2.9, "Miscellaneous," on page 260

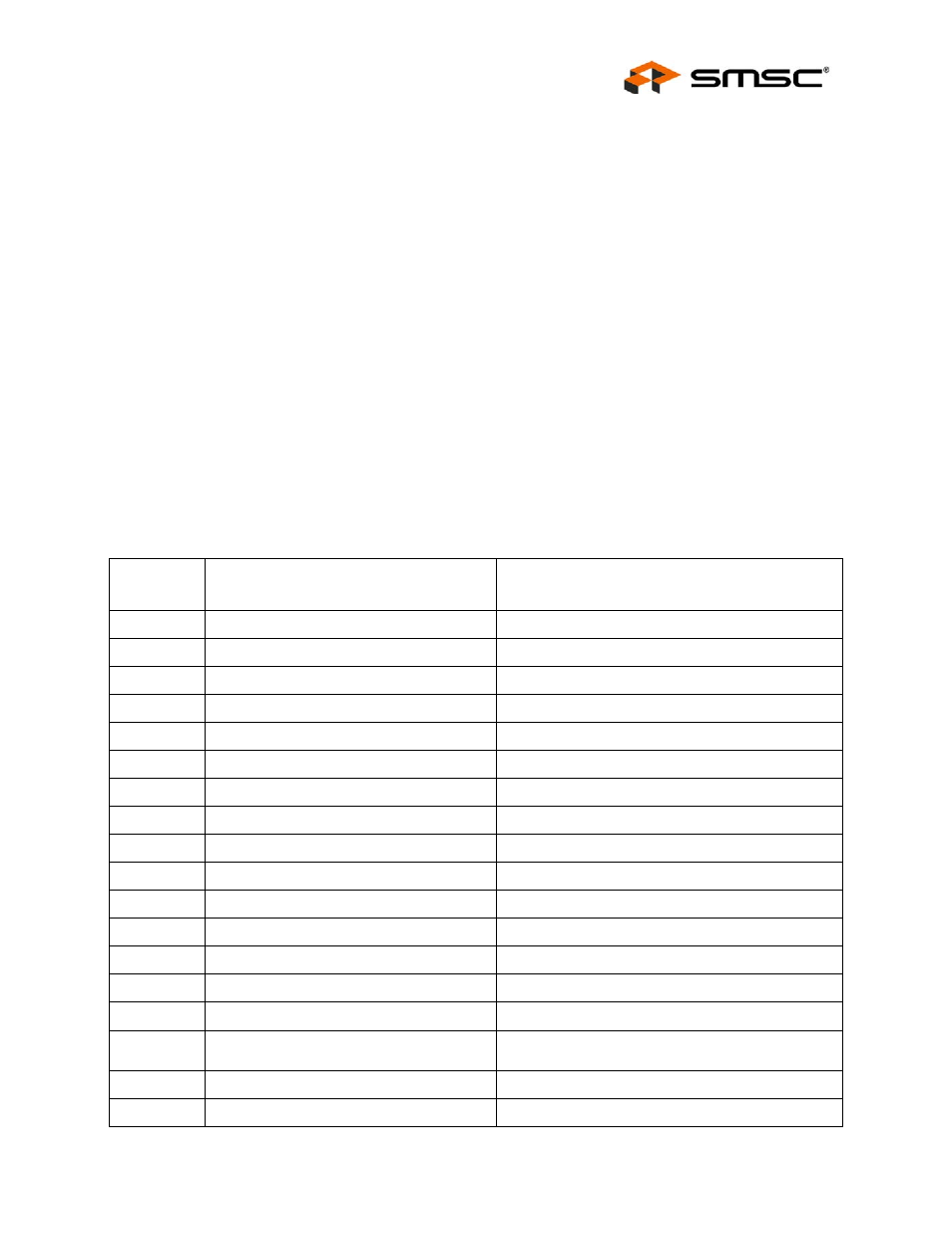

Table 14.1 System Control and Status Registers

ADDRESS

OFFSET

SYMBOL

REGISTER NAME

050h

ID_REV

Chip ID and Revision Register,

054h

IRQ_CFG

Interrupt Configuration Register,

058h

INT_STS

Interrupt Status Register,

05Ch

INT_EN

Interrupt Enable Register,

060h

RESERVED

Reserved for Future Use

064h

BYTE_TEST

Byte Order Test Register,

068h

FIFO_INT

FIFO Level Interrupts Register,

06Ch

RX_CFG

Receive Configuration Register,

070h

TX_CFG

Transmit Configuration Register,

074h

HW_CFG

Hardware Configuration Register,

078h

RX_DP_CTRL

RX Datapath Control Register,

07Ch

RX_FIFO_INF

Receive FIFO Information Register,

080h

TX_FIFO_INF

Transmit FIFO Information Register,

084h

PMT_CTRL

Power Management Control Register,

088h

RESERVED

Reserved for Future Use

08Ch

GPT_CFG

General Purpose Timer Configuration Register,

090h

GPT_CNT

General Purpose Timer Count Register,

094h - 098h

RESERVED

Reserved for Future Use