3 gpio/led, Ng the, General purpose i/o configuration – SMSC LAN9311i User Manual

Page 193: Register (gpio_cfg), General purpose i/o, Configuration register (gpio_cfg), Section, Push/p, Section 14.2.3.1, Datasheet 14.2.3 gpio/led

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i

193

Revision 1.4 (08-19-08)

DATASHEET

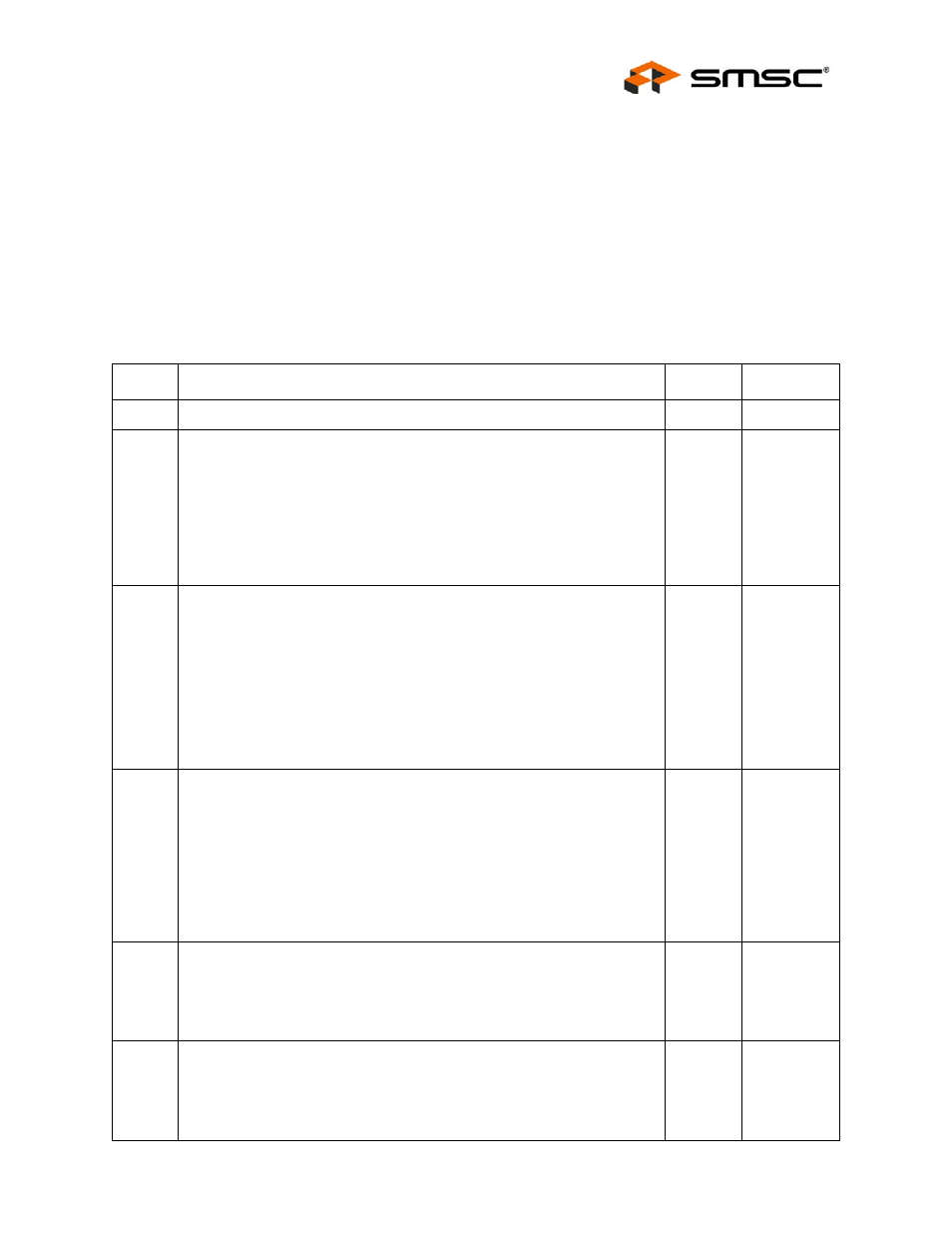

14.2.3

GPIO/LED

This section details the General Purpose I/O (GPIO) and LED related System CSR’s.

14.2.3.1

General Purpose I/O Configuration Register (GPIO_CFG)

This read/write register configures the GPIO input and output pins. The polarity of the 12 GPIO pins

is configured here as well as the IEEE 1588 timestamping and clock compare event output properties

of the GPIO[9:8] pins.

Offset:

1E0h

Size:

32 bits

BITS

DESCRIPTION

TYPE

DEFAULT

31:30

RESERVED

RO

-

29:28

GPIO 1588 Timer Interrupt Clear Enable 9-8

(GPIO_1588_TIMER_INT_CLEAR_EN[9:8])

These bits enable inputs on GPIO9 and GPIO8 to clear the

1588_TIMER_INT bit of the

1588 Interrupt Status and Enable Register

. The polarity of these inputs is determined by

GPIO_INT_POL[9:8].

Note:

The GPIO must be configured as an input for this function to

operate. For the clear function, GPIO inputs are edge sensitive and

must be active for greater than 40 nS to be recognized.

R/W

00b

27:16

GPIO Interrupt Polarity 11-0 (GPIO_INT_POL[11:0])

These bits set the interrupt polarity of the 12 GPIO pins. The configured

level (high/low) will set the corresponding GPIO_INT bit in the

Purpose I/O Interrupt Status and Enable Register (GPIO_INT_STS_EN)

.

0: Sets low logic level trigger on corresponding GPIO pin

1: Sets high logic level trigger on corresponding GPIO pin

GPIO_INT_POL[9:8] also determines the polarity of the GPIO IEEE 1588

time clock capture events and the GPIO 1588 Timer Interrupt Clear inputs.

Refer to

Section 13.2, "GPIO Operation," on page 163

for additional

information.

R/W

0h

15:14

1588 GPIO Output Enable 9-8 (1588_GPIO_OE[9:8])

These bits configure GPIO 9 and GPIO 8 to output 1588 clock compare

events.

0: Disables the output of 1588 clock compare events

1: Enables the output of 1588 clock compare events

Note:

These bits override the direction bits in the

Data & Direction Register (GPIO_DATA_DIR)

register. However,

the GPIO buffer type (GPIOBUF[11:0]) in the

Configuration Register (GPIO_CFG)

is not overridden.

R/W

0h

13

GPIO 9 Clock Event Polarity (GPIO_EVENT_POL_9)

This bit determines if the 1588 clock event output on GPIO 9 is active high

or low.

0: 1588 clock event output active low

1: 1588 clock event output active high

R/W

1b

12

GPIO 8 Clock Event Polarity (GPIO_EVENT_POL_8)

This bit determines if the 1588 clock event output on GPIO 8 is active high

or low.

0: 1588 clock event output active low

1: 1588 clock event output active high

R/W

1b