Section 14.5.2.38, Datasheet – SMSC LAN9311i User Manual

Page 361

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i

361

Revision 1.4 (08-19-08)

DATASHEET

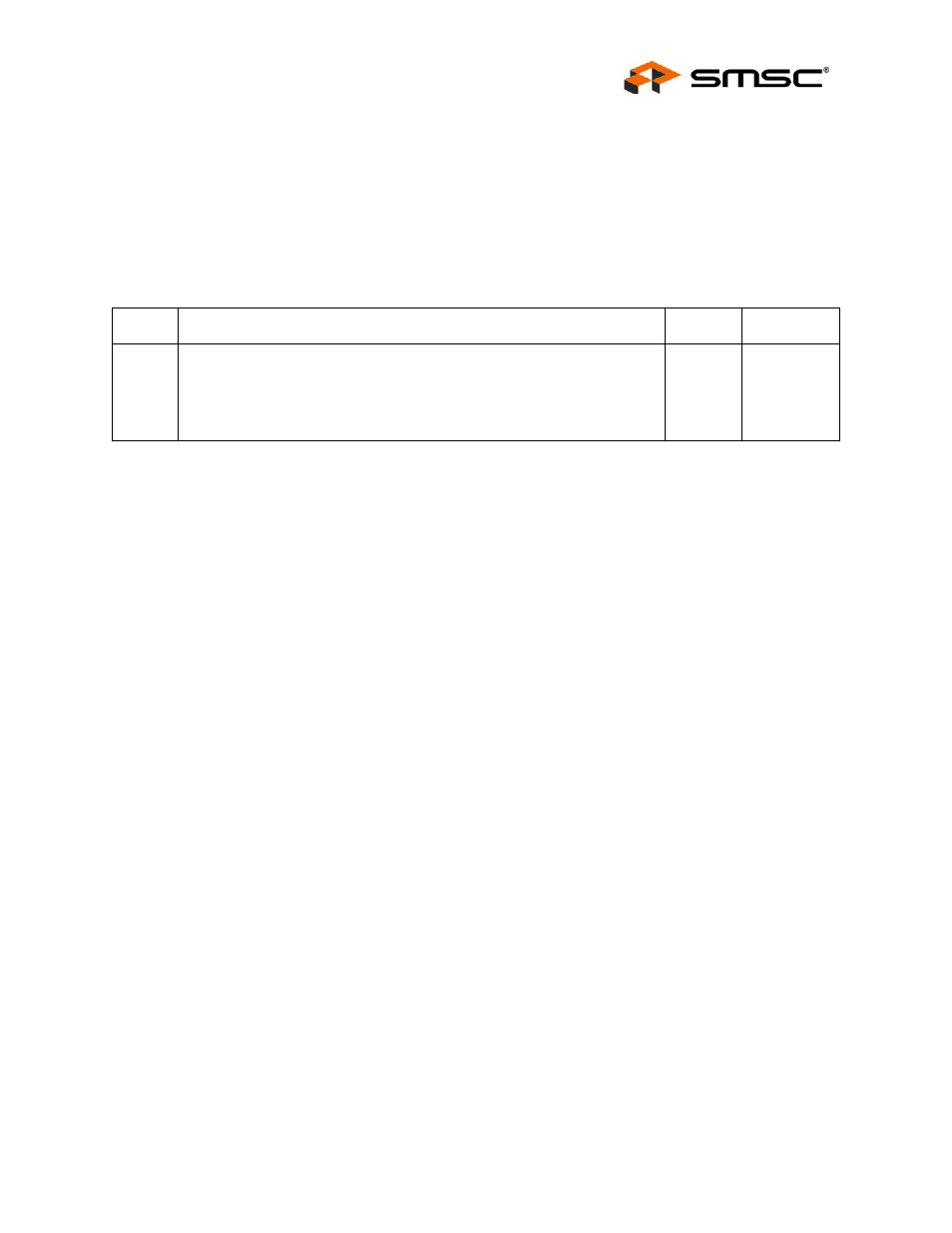

14.5.2.38

Port x MAC Transmit Late Collision Count Register (MAC_TX_LATECOL_CNT_x)

This register provides a counter of transmitted packets which experienced a late collision. The counter

is cleared upon being read.

Register #:

Port0: 045Fh

Size:

32 bits

Port1: 085Fh

Port2: 0C5Fh

BITS

DESCRIPTION

TYPE

DEFAULT

31:0

TX Late Collision

Count of transmitted packets that experienced a late collision. This counter

is incremented only in half-duplex operation.

Note:

This counter will stop at its maximum value of FFFF_FFFFh.

Minimum rollover time at 100Mbps is approximately 481 hours.

RC

00000000h

This manual is related to the following products: