Section 14.5.3.20, Datasheet – SMSC LAN9311i User Manual

Page 390

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08)

390

SMSC LAN9311/LAN9311i

DATASHEET

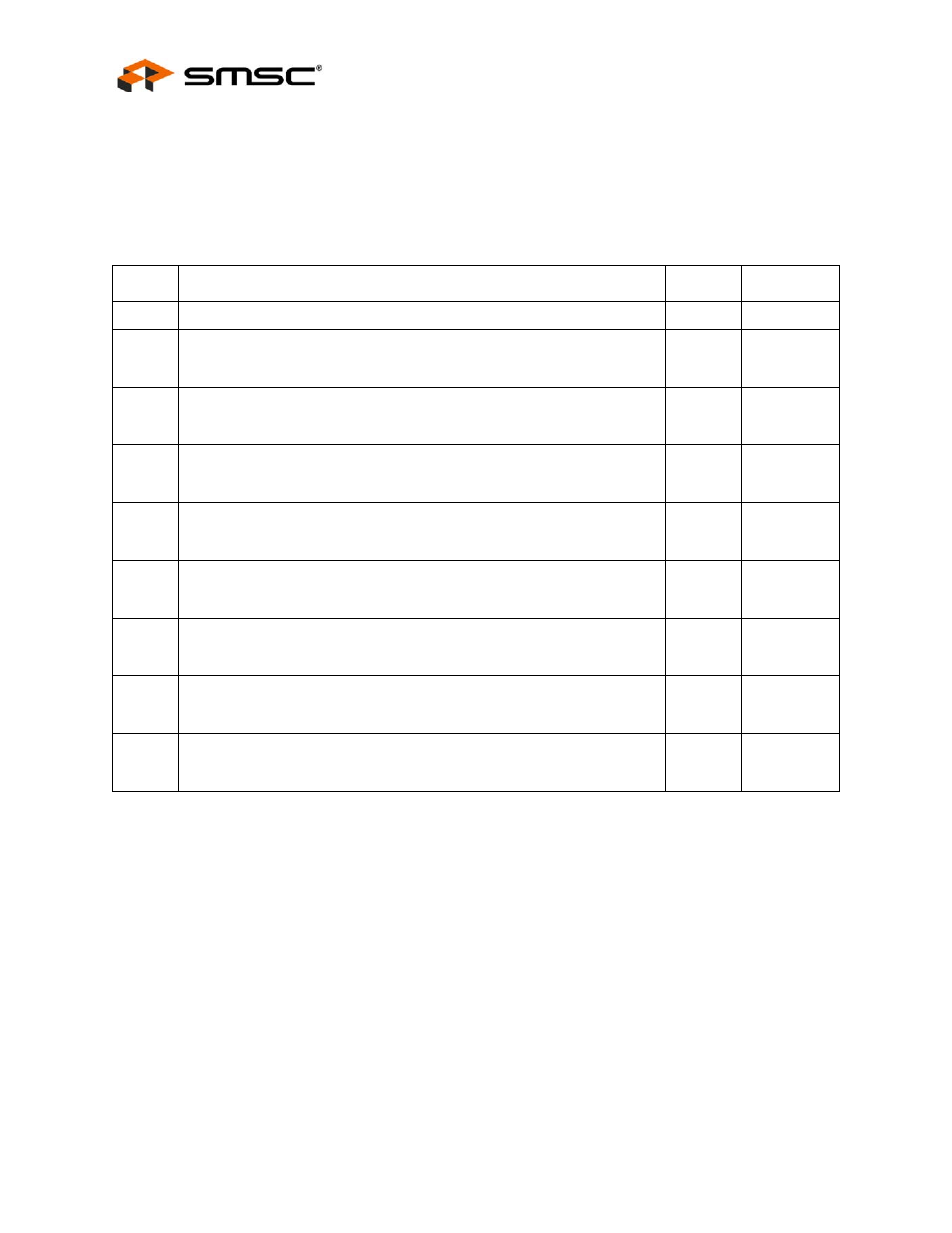

14.5.3.20

Switch Engine Priority to Queue Register (SWE_PRI_TO_QUE)

This register specifies the Traffic Class table that maps the packet priority into the egress queues.

Register #:

1845h

Size:

32 bits

BITS

DESCRIPTION

TYPE

DEFAULT

31:16

RESERVED

RO

-

15:14

Priority 7 traffic Class

These bits specify the egress queue that is used for packets with a priority

of 7.

R/W

11b

13:12

Priority 6 traffic Class

These bits specify the egress queue that is used for packets with a priority

of 6.

R/W

11b

11:10

Priority 5 traffic Class

These bits specify the egress queue that is used for packets with a priority

of 5.

R/W

10b

9:8

Priority 4 traffic Class

These bits specify the egress queue that is used for packets with a priority

of 4.

R/W

10b

7:6

Priority 3 traffic Class

These bits specify the egress queue that is used for packets with a priority

of 3.

R/W

01b

5:4

Priority 2 traffic Class

These bits specify the egress queue that is used for packets with a priority

of 2.

R/W

00b

3:2

Priority 1 traffic Class

These bits specify the egress queue that is used for packets with a priority

of 1.

R/W

00b

1:0

Priority 0 traffic Class

These bits specify the egress queue that is used for packets with a priority

of 0.

R/W

01b