7 rx data fifo direct pio burst reads, Rx data fifo direct pio burst reads – SMSC LAN9311i User Manual

Page 110

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08)

110

SMSC LAN9311/LAN9311i

DATASHEET

8.5.7

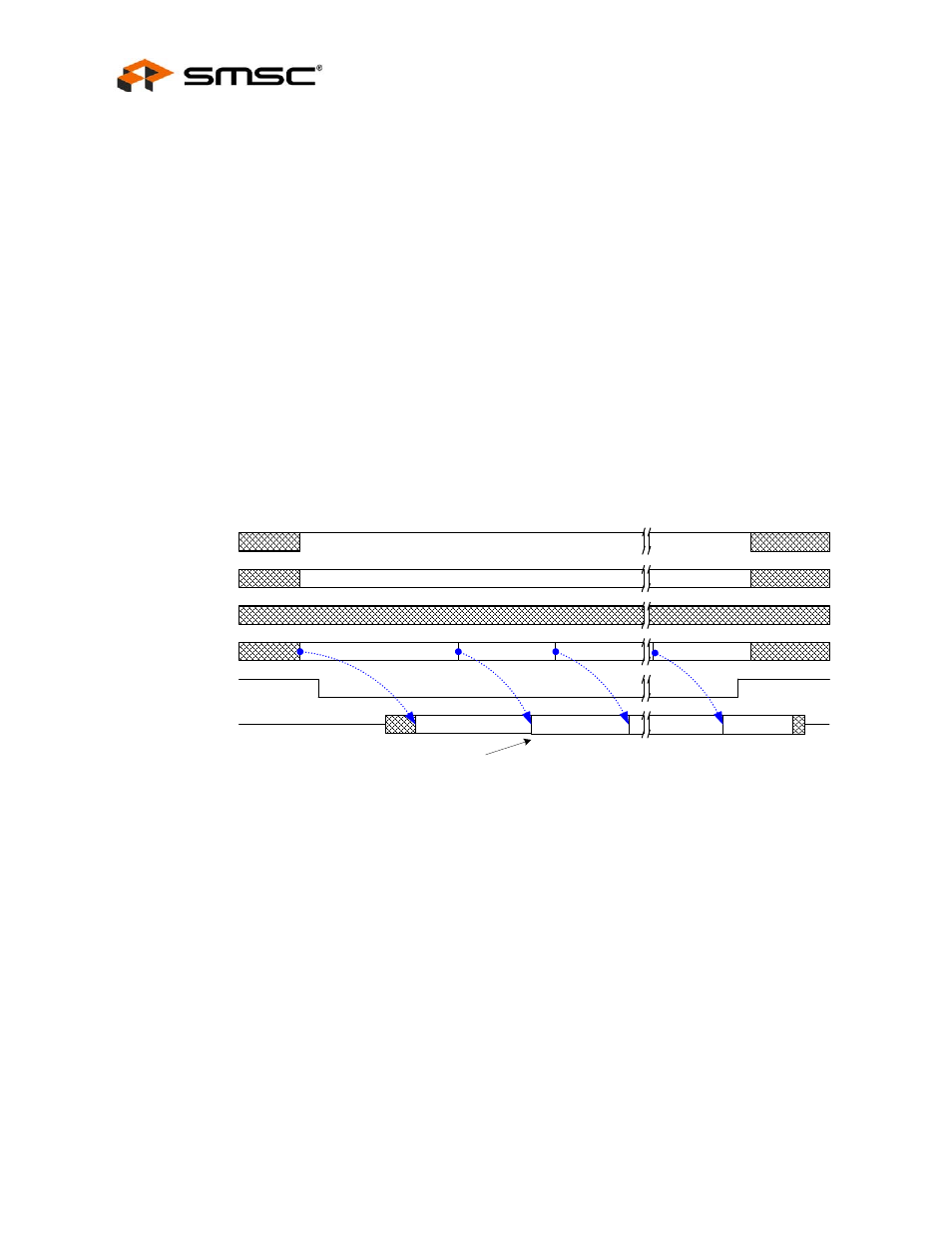

RX Data FIFO Direct PIO Burst Reads

In this mode only A[2:1] are decoded, and any burst read of the LAN9311/LAN9311i will read the RX

Data FIFO. This mode is enabled when FIFO_SEL is driven high during a read access. This is normally

accomplished by connecting the FIFO_SEL signal to a high-order address line. This mode is useful

when the host processor must increment its address when accessing the LAN9311/LAN9311i. Timing

is identical to a PIO burst read, and the FIFO_SEL and END_SEL signals have the same timing

characteristics as the address lines.

In this mode, performance is improved by allowing an unlimited number of back-to-back WORD read

cycles. RX Data FIFO direct PIO burst reads can be performed using chip select (nCS) or read enable

(nRD). An RX Data FIFO direct PIO burst read begins when both nCS and nRD are asserted. Either

or both of these control signals must de-assert between bursts for the period specified in

“RX Data FIFO Direct PIO Burst Read Cycle Timing Values,” on page 451

. The burst cycle ends when

either or both nCS and nRD are de-asserted. They may be asserted and de-asserted in any order.

Read data is valid as indicated in the functional timing diagram in

.

Note:

A[1] must toggle during burst reads. Fresh data is supplied each time A[1] is toggled.

Please refer to

Section 15.5.7, "RX Data FIFO Direct PIO Burst Read Cycle Timing," on page 451

for

the AC timing specifications for PIO RX Data FIFO direct PIO burst read operations.

Figure 8.6 Functional Timing for RX Data FIFO Direct PIO Burst Read Operation

END_SEL

A[x:3]

A[2:1]

nCS, nRD

D[15:0] (OUTPUT)

FIFO_SEL

(READ DATA FROM RX DATA FIFO)