3 power management, Power management, Table 4.3 – SMSC LAN9311i User Manual

Page 46: Provid, Datasheet

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08)

46

SMSC LAN9311/LAN9311i

DATASHEET

4.3

Power Management

The LAN9311/LAN9311i Port 1 and Port 2 PHYs and the Host MAC support several power

management and wakeup features.

The LAN9311/LAN9311i can be programmed to issue an external wake signal (PME) via several

methods, including wake on LAN, wake on link status change (energy detect), and magic packet

wakeup. The PME signal is ideal for triggering system power-up using remote Ethernet wakeup events.

A simplified diagram of the logic that controls the PME and PME_INT signals can be seen in

.

The PME module handles the latching of the Port 1 & 2 PHY Energy-Detect Status (ED_STS1 and

ED_STS2) and Wake-On LAN Status (WOL_STS) bits of the

Power Management Control Register

. This module also masks the status bits with the corresponding enable bits (ED_EN1,

ED_EN2, WOL_EN) and combines the results together to generate the PME_INT status bit in the

Interrupt Status Register (INT_STS)

. The PME_INT status bit is then masked with the PME_EN bit and

conditioned before becoming the PME output pin.

The PME output characteristics can be configured via the PME_TYPE, PME_IND, and PME_POL bits

of the

Power Management Control Register (PMT_CTRL)

. These bits allow the PME to be open-drain,

active high push-pull, or active-low push-pull and configure the output to be continuous, or pulse for

50mS.

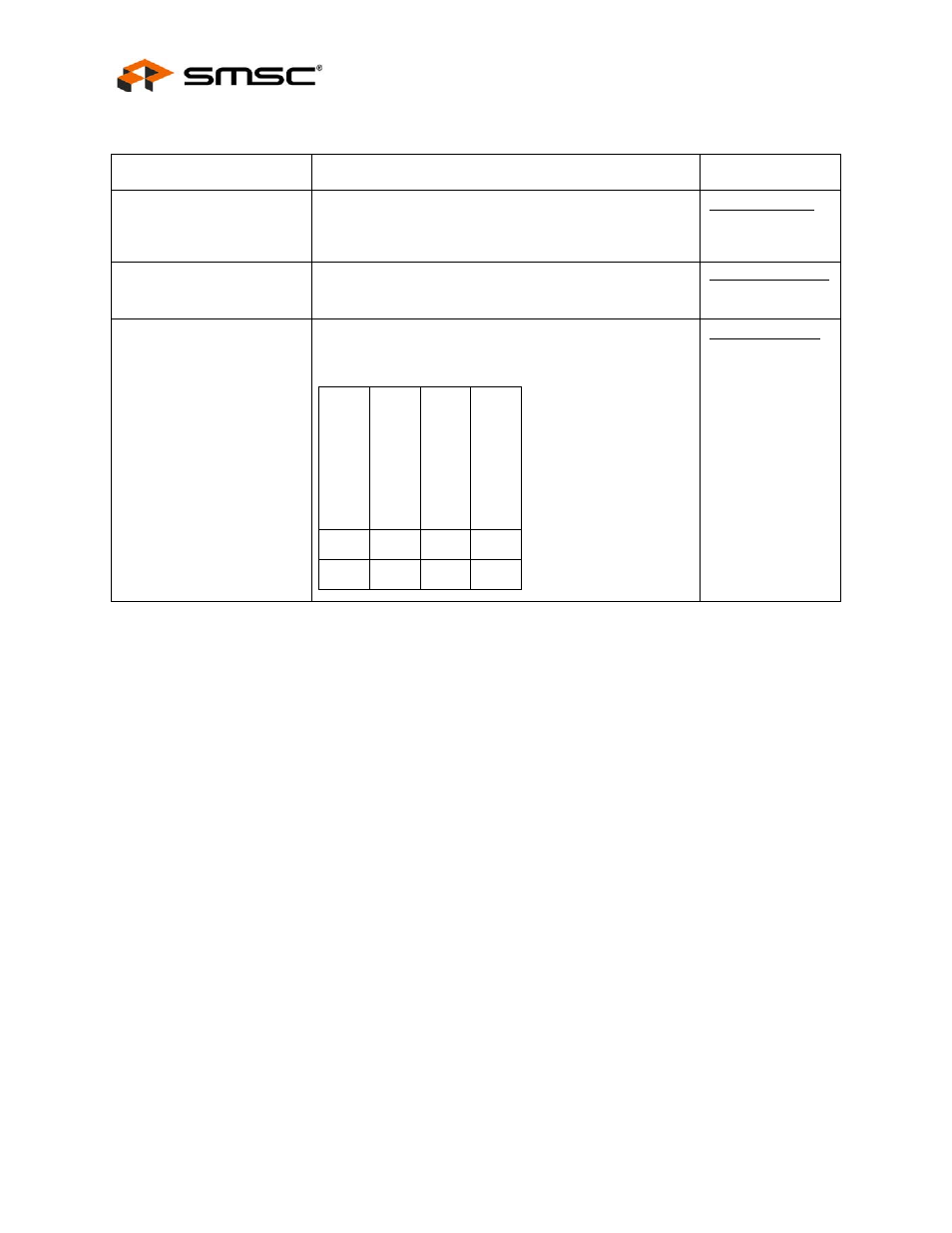

Table 4.3 Hard-Strap Configuration Strap Definitions

STRAP NAME

DESCRIPTION

PIN

eeprom_type_strap

EEPROM Type Strap: Configures the EEPROM type.

0 = Microwire Mode

1 = I

2

C Mode

EEPROM_TYPE

eeprom_size_strap[1:0]

EEPROM Size Strap [1:0]: Configures the EEPROM size

range as specified in

Section 10.2, "I2C/Microwire Master

EEPROM Controller," on page 138

.

EEPROM_SIZE_[1:0]

phy_addr_sel_strap

PHY Address Select Strap: Configures the default MII

management address values for the PHYs and Virtual PHY

as detailed in

Section 7.1.1, "PHY Addressing," on page 82

PHY_ADDR_SEL

P

H

Y

_

ADDR_SEL_

S

TRA

P

VALUE

V

IRT

UAL PHY

ADDRESS

PO

R

T

1

P

H

Y

ADDRESS

PO

R

T

2

P

H

Y

ADDRESS

0

0

1

2

1

1

2

3