Phy management interface access, Register (pmi_access), Access only) – SMSC LAN9311i User Manual

Page 245: Section 14.2.7.2, Phy management interface access register, Pmi_access), Datasheet

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i

245

Revision 1.4 (08-19-08)

DATASHEET

14.2.7.2

PHY Management Interface Access Register (PMI_ACCESS)

This register is used to control the management cycles to the PHYs. A PHY access is initiated when

this register is written. This register is used in conjunction with the

to perform write operations to the PHYs.

Note:

This register is only accessible by the EEPROM Loader and NOT by the Host bus. Refer to

Section 10.2.4, "EEPROM Loader," on page 150

for additional information.

Offset:

0A8h

EEPROM Loader

Access Only

Size:

32 bits

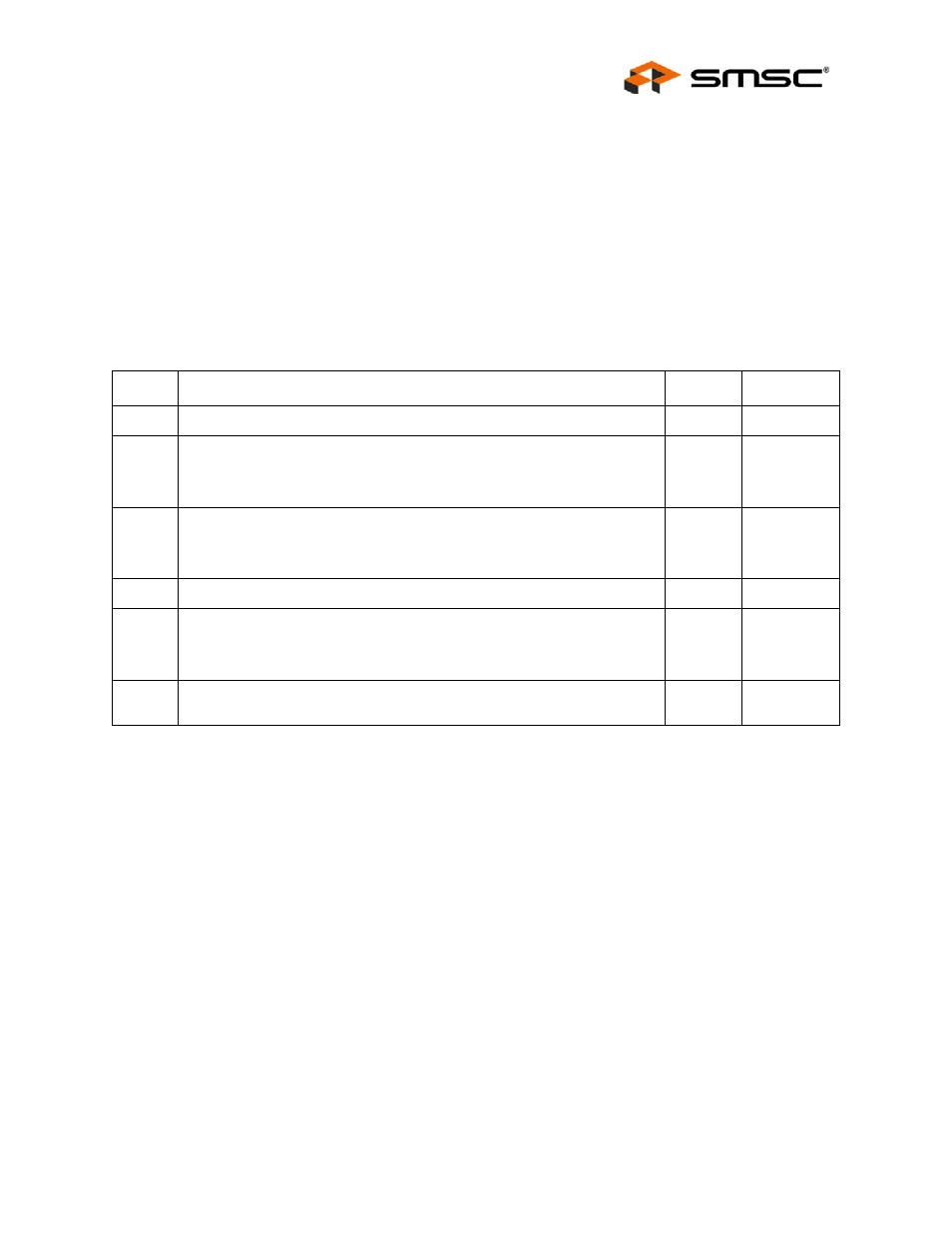

BITS

DESCRIPTION

TYPE

DEFAULT

31:16

RESERVED

RO

-

15:11

PHY Address (PHY_ADDR)

These bits select the PHY device being accessed. Refer to

for information on PHY address

assignments.

WO

00000b

10:6

MII Register Index (MIIRINDA)

These bits select the desired MII register in the PHY. Refer to

"Ethernet PHY Control and Status Registers," on page 287

for detailed

descriptions on all PHY registers.

WO

00000b

5:2

RESERVED

RO

-

1

RESERVED

Note:

This bit must always be written with a value of 1.

WO

0b

0

RESERVED

RO

0b