1 tx buffer format, Figure 9.4 tx buffer format, 2 tx command format – SMSC LAN9311i User Manual

Page 125: Tx buffer format, Tx command format, Datasheet 9.8.1 tx buffer format

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i

125

Revision 1.4 (08-19-08)

DATASHEET

9.8.1

TX Buffer Format

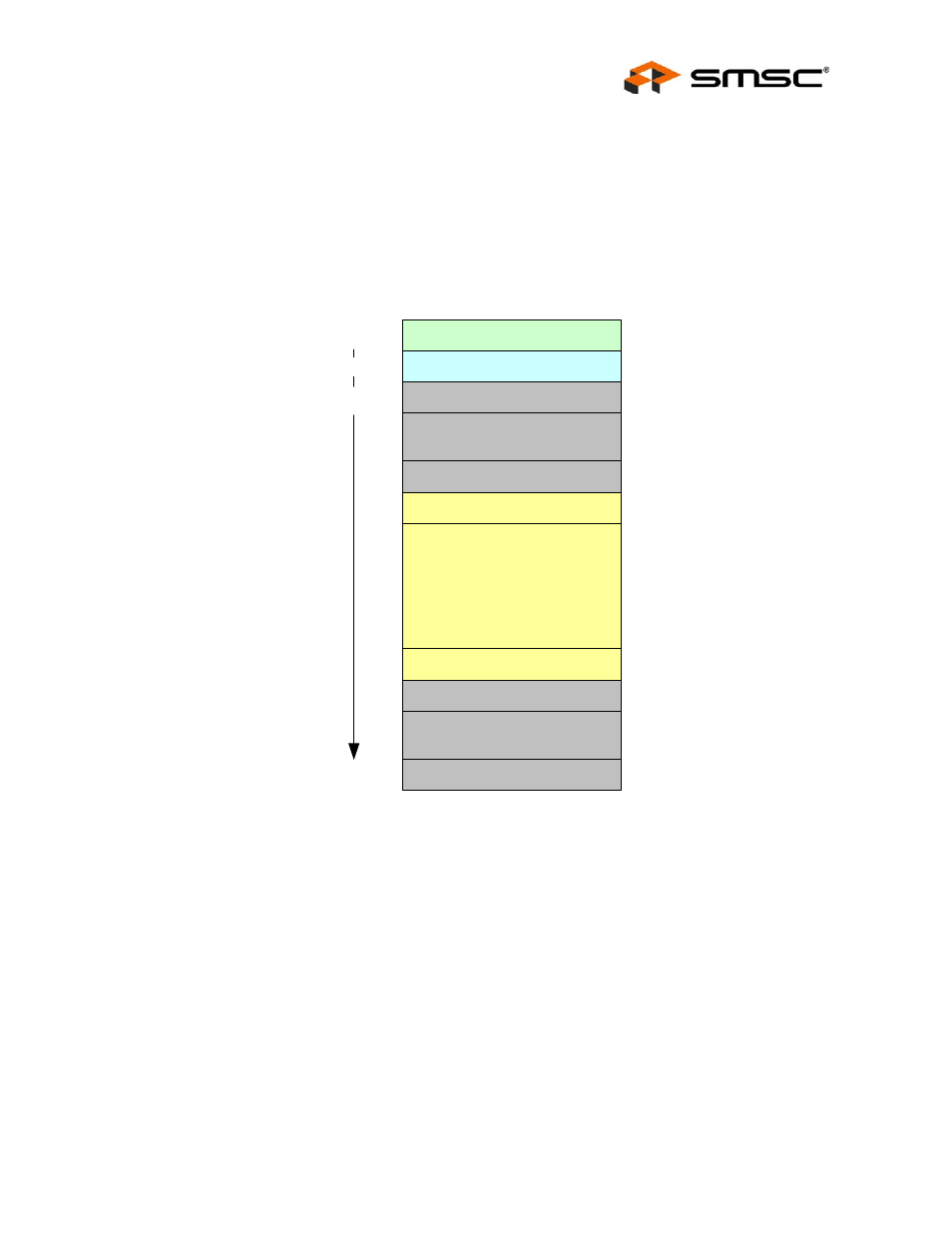

TX buffers exist in the host’s memory in a given format. The host writes a TX command word into the

TX data buffer before moving the Ethernet packet data. The TX command A and command B are 32-

bit values that are used by the LAN9311/LAN9311i in the handling and processing of the associated

Ethernet packet data buffer. Buffer alignment, segmentation and other packet processing parameters

are included in the command structure. The buffer format is illustrated in

shows the TX Buffer as it is written into the LAN9311/LAN9311i. It should be noted that not

all of the data shown in this diagram is actually stored in the TX Data FIFO. This must be taken into

account when calculating the actual TX Data FIFO usage. Please refer to

for a detailed explanation on calculating the actual TX Data FIFO usage.

9.8.2

TX Command Format

The TX command instructs the TX FIFO controller on handling the subsequent buffer. The command

precedes the data to be transmitted. The TX command is divided into two, 32-bit words; TX command

‘A’ and TX command ‘B’.

There is a 16-bit Packet Tag in the TX command ‘B’ command word. Packet Tags may, if host software

desires, be unique for each packet (i.e., an incrementing count). The value of the tag will be returned

in the TX status word for the associated packet. The Packet tag can be used by host software to

uniquely identify each status word as it is returned to the host.

Figure 9.4 TX Buffer Format

TX Command 'A'

Offset + Data DWORD0

.

.

.

.

.

Last Data & PAD

0

31

1st

2nd

3rd

Last

Host Write

Order

Optional Pad DWORD0

.

.

.

Optional Pad DWORDn

TX Command 'B'

Optional offset DWORD0

.

.

.

Optional offset DWORDn