4 fifo level interrupt register (fifo_int), Fifo level interrupt register (fifo_int), Section 14.2.1.4 – SMSC LAN9311i User Manual

Page 180: Tx data available level, Field, Tx status level, Fifo level interrupt, Register (fifo_int), Rx status level, Datasheet

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08)

180

SMSC LAN9311/LAN9311i

DATASHEET

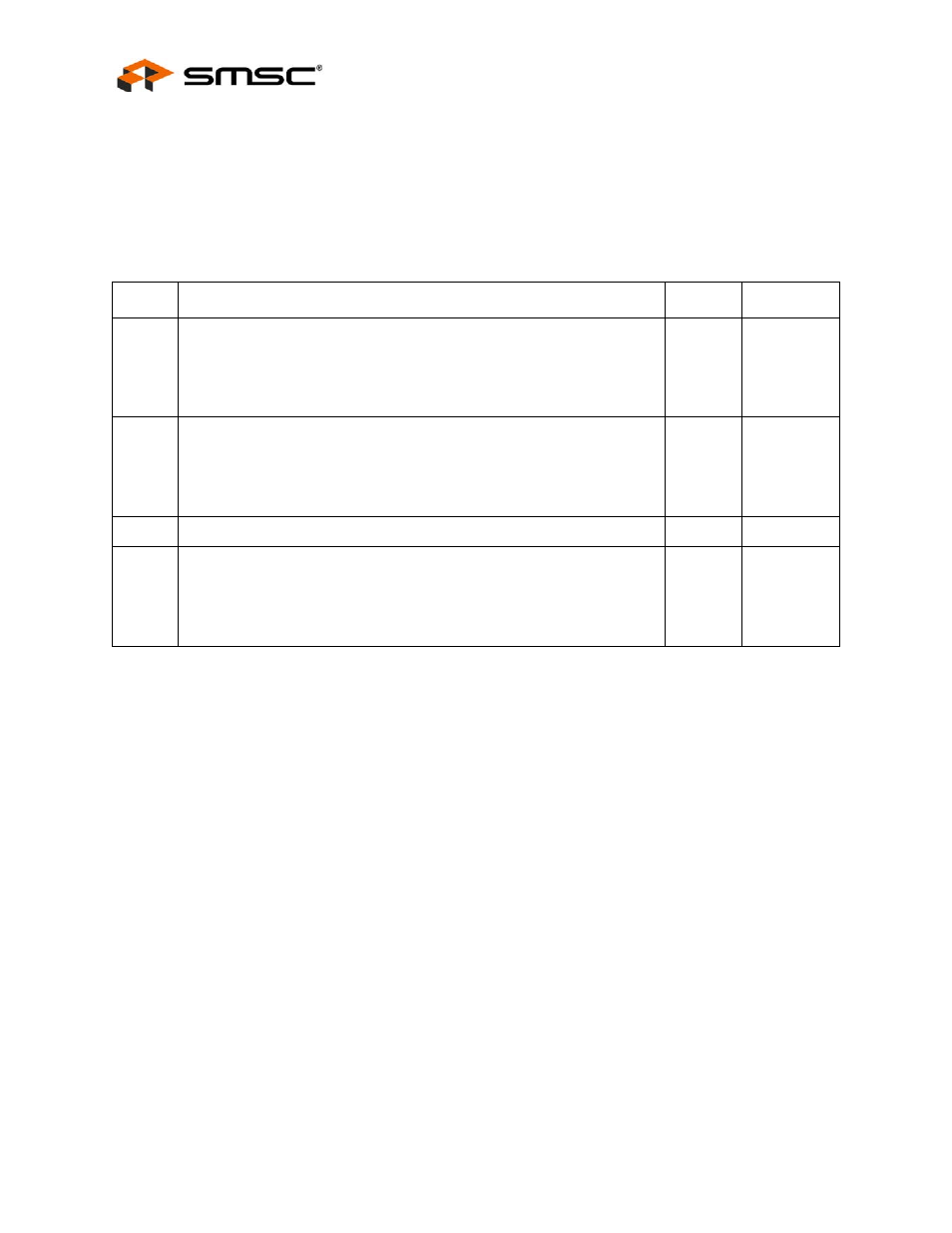

14.2.1.4

FIFO Level Interrupt Register (FIFO_INT)

This read/write register configures the limits where the RX/TX Data and Status FIFO’s will generate

system interrupts.

Offset:

068h

Size:

32 bits

BITS

DESCRIPTION

TYPE

DEFAULT

31:24

TX Data Available Level

The value in this field sets the level, in number of 64 Byte blocks, at which

the

TX Data FIFO Available Interrupt (TDFA)

TX Data FIFO free space is greater than this value, a

R/W

48h

23:16

TX Status Level

The value in this field sets the level, in number of DWORD’s, at which the

TX Status FIFO Level Interrupt (TSFL)

will be generated. When the TX

Status FIFO used space is greater than this value, a

will be generated in the

R/W

00h

15:8

RESERVED - This field must be written with 00h for proper operation.

R/W

00h

7:0

RX Status Level

The value in this field sets the level, in number of DWORD’s, at which the

RX Status FIFO Level Interrupt (RSFL)

will be generated. When the RX

Status FIFO used space is greater than this value, a

will be generated in the

R/W

00h