1588_clock_hi_tx_capture_x), Section 14.2.5.5, Datasheet – SMSC LAN9311i User Manual

Page 206

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08)

206

SMSC LAN9311/LAN9311i

DATASHEET

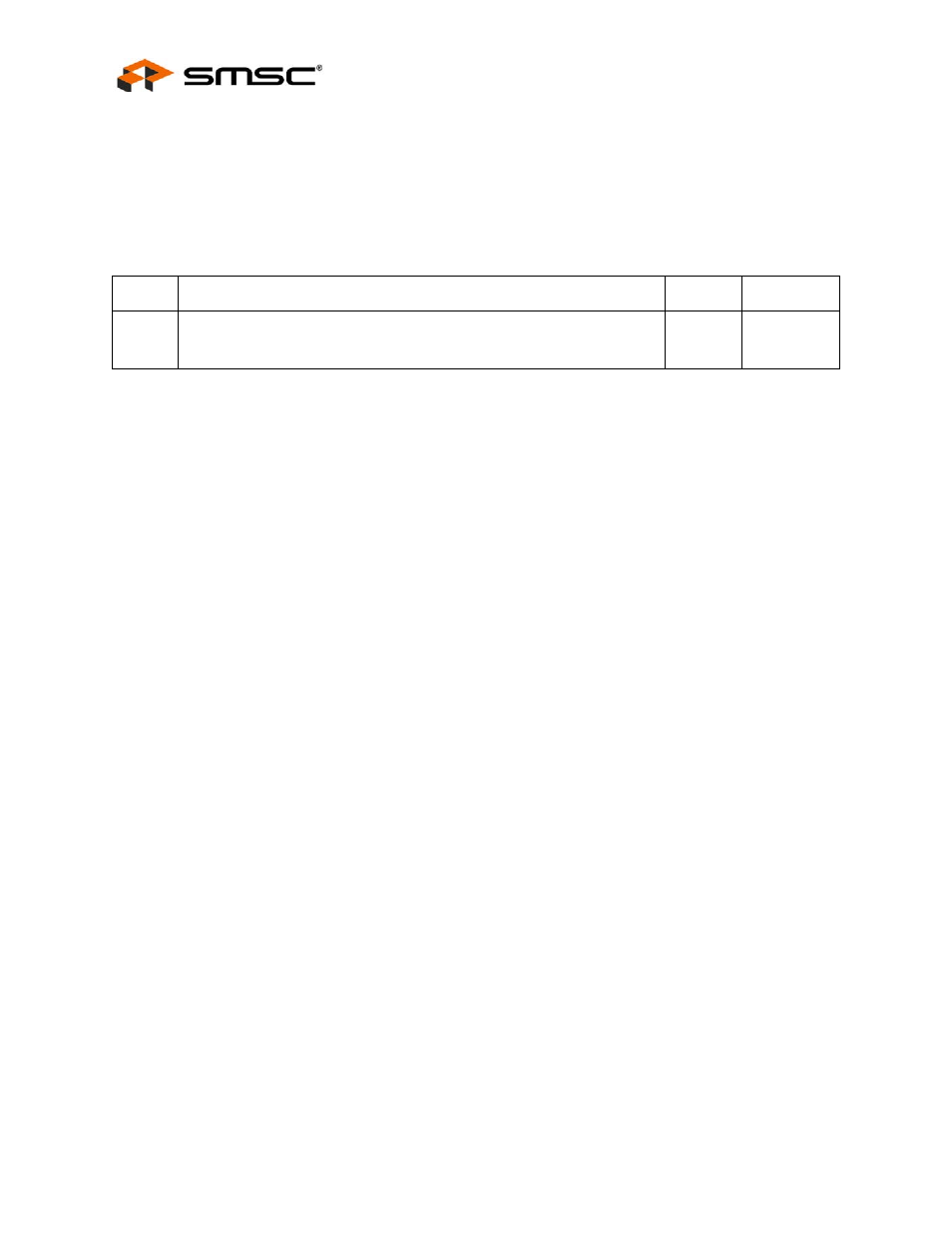

14.2.5.5

Port x 1588 Clock High-DWORD Transmit Capture Register (1588_CLOCK_HI_TX_CAPTURE_x)

Note:

The selection between Sync or Delay_Req packets is based on the corresponding

master/slave bit in the

1588 Configuration Register (1588_CONFIG)

Note:

There are multiple instantiations of this register, one for each port of the LAN9311/LAN9311i.

Refer to

for additional information.

Note:

For Port 0(Host MAC), receive is defined as data from the switch fabric, while transmit is to

the switch fabric.

Offset:

Port 1: 110h

Size:

32 bits

Port 2: 130h

Port 0: 150h

BITS

DESCRIPTION

TYPE

DEFAULT

31:0

Timestamp High (TS_HI)

This field contains the high 32-bits of the timestamp taken on the

transmission of a 1588 Sync or Delay_Req packet.

RO

00000000h