Host mac, Csr interface data register (mac_csr_data), System regis – SMSC LAN9311i User Manual

Page 189: Section 14.2.2.8, Datasheet

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i

189

Revision 1.4 (08-19-08)

DATASHEET

14.2.2.8

Host MAC CSR Interface Data Register (MAC_CSR_DATA)

This read-write register is used in conjunction with the

Host MAC CSR Interface Command Register

to indirectly access the Host MAC CSR’s.

Note:

The full list of Host MAC CSR’s are described in

Section 14.3, "Host MAC Control and Status

. For more information on the Host MAC, refer to

.

Offset:

0A8h

Size:

32 bits

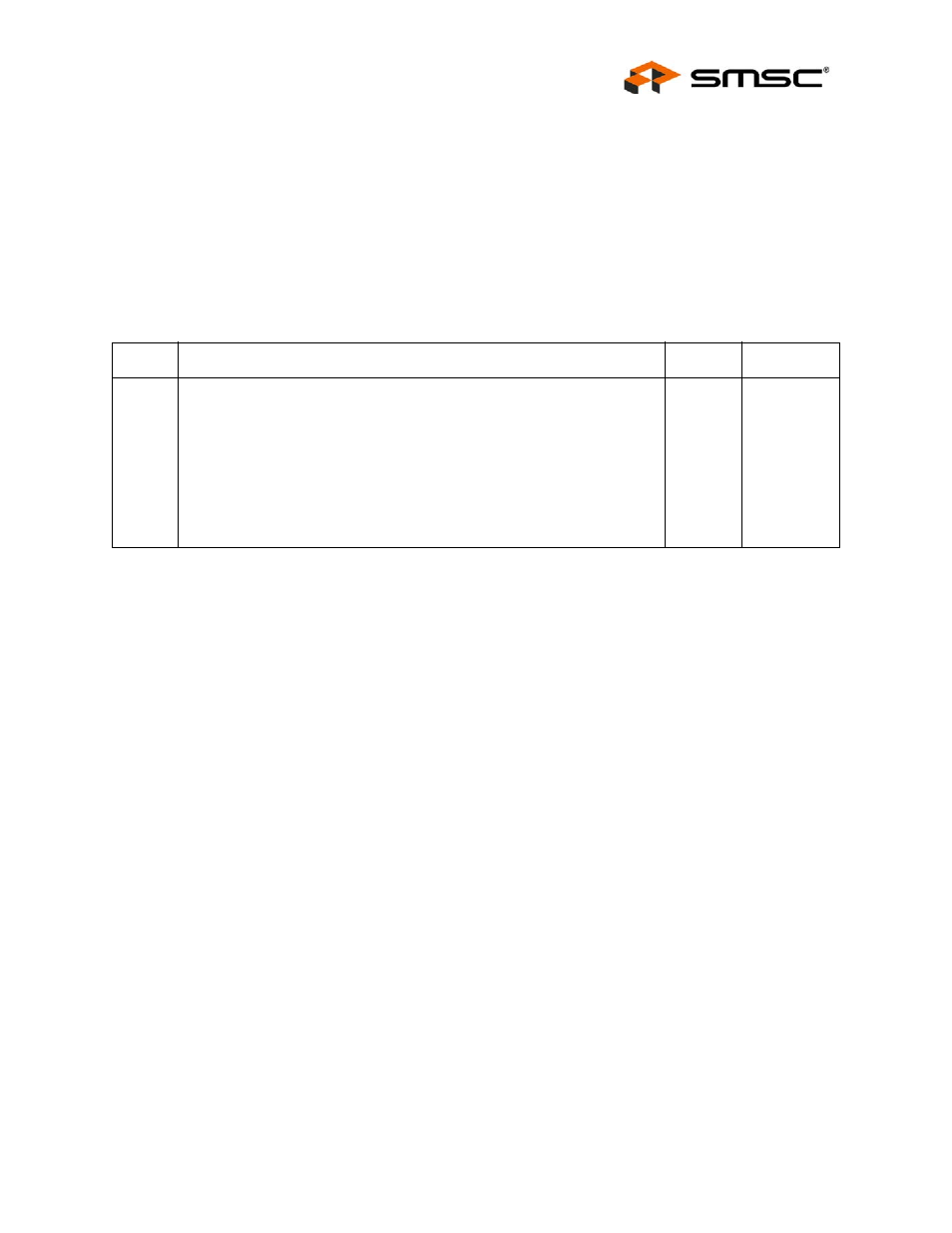

BITS

DESCRIPTION

TYPE

DEFAULT

31:0

Host MAC CSR Data

This field contains the value read from or written to the Host MAC CSR as

specified in the

Host MAC CSR Interface Command Register

. Upon a read, the value returned depends on the R/nW

bit in the MAC_CSR_CMD register. If R/nW is a 1, the data in this register

is from the Host MAC. If R/nW is 0, the data is the value that was last written

into this register.

Note:

The MAC_CSR_CMD and MAC_CSR_DATA registers must not be

modified until the CSR Busy bit is cleared in the MAC_CSR_CMD

register.

R/W

00000000h