3 receive datapath control register (rx_dp_ctrl), Receive datapath control register (rx_dp_ctrl), Section 14.2.2.3 – SMSC LAN9311i User Manual

Page 184: Datasheet

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08)

184

SMSC LAN9311/LAN9311i

DATASHEET

14.2.2.3

Receive Datapath Control Register (RX_DP_CTRL)

This register is used to discard unwanted receive frames.

Offset:

078h

Size:

32 bits

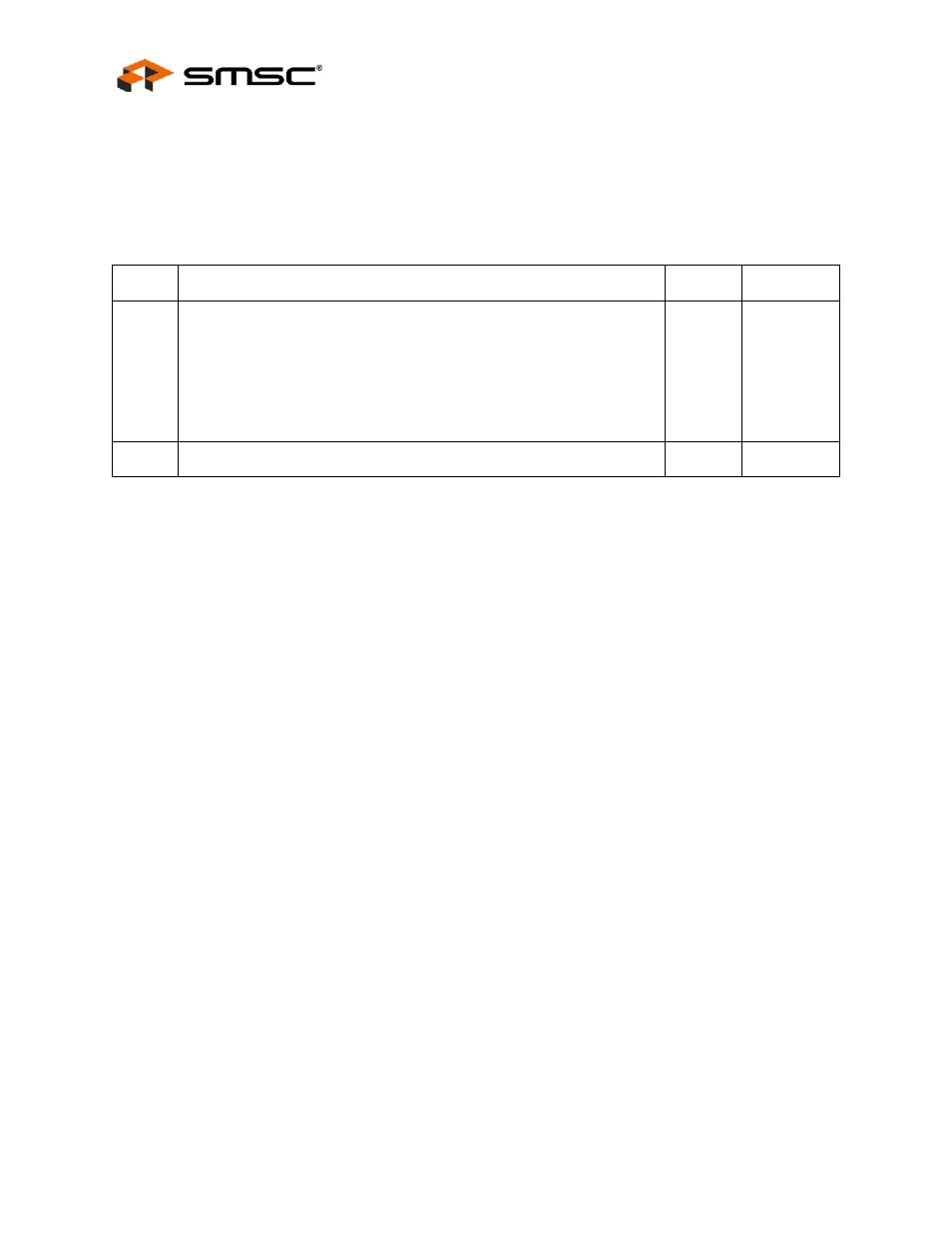

BITS

DESCRIPTION

TYPE

DEFAULT

31

RX Data FIFO Fast Forward (RX_FFWD)

Writing a 1 to this bit causes the RX Data FIFO to fast-forward to the start

of the next frame. This bit will remain high until the RX Data FIFO fast-

forward operation has completed. No reads should be issued to the RX Data

FIFO while this bit is high.

Note:

Please refer to section

Section 9.9.1.1, "Receive Data FIFO Fast

for detailed information regarding the use

of RX_FFWD.

R/W

SC

0h

30:0

RESERVED

RO

-

This manual is related to the following products: