2 ieee 1588 time stamp, Table 11.1 ieee 1588 message type detection, Figure 11.2 ieee 1588 message time stamp point – SMSC LAN9311i User Manual

Page 157: Ieee 1588 time stamp

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i

157

Revision 1.4 (08-19-08)

DATASHEET

11.2

IEEE 1588 Time Stamp

The LAN9311/LAN9311i contains three identical IEEE 1588 Time Stamp blocks as shown in

. These blocks are responsible for capturing the source UUID, sequence ID, and current

64-bit IEEE 1588 clock time upon detection of a Sync or Delay_Req message type on their respective

port. The mode of the clock (master or slave) determines which message is detected on receive and

transmit. For slave clock operation, Sync messages are detected on receive and Delay_Req messages

on transmit. For master clock operation, Delay_Req messages are detected on receive and Sync

messages on transmit. Follow_Up, Delay_Resp and Management packet types do not cause capture.

Each port may be individually configured as an IEEE 1588 master or slave clock via the master/slave

bits (M_nS_1 for Port 1, MnS_2 for Port2, and M_nS_MII for Port 0) in the

summarizes the message type detection under slave and master IEEE

1588 clock operation.

For ports 1 and 2, receive is defined as data from the PHY (from the outside world) and transmit is

defined as data to the PHY. This is consistent with the point-of-view of where the partner clock resides

(LAN9311/LAN9311i receives packets from the partner via the PHY, etc.). For the time stamp module

connected to the Host MAC (Port 0), the definition of transmit and receive is reversed. Receive is

defined as data from the switch fabric, while transmit is defined as data to the switch fabric. This is

consistent with the point-of-view of where the partner clock resides (LAN9311/LAN9311i receives

packets from the partner via the switch fabric, etc.).

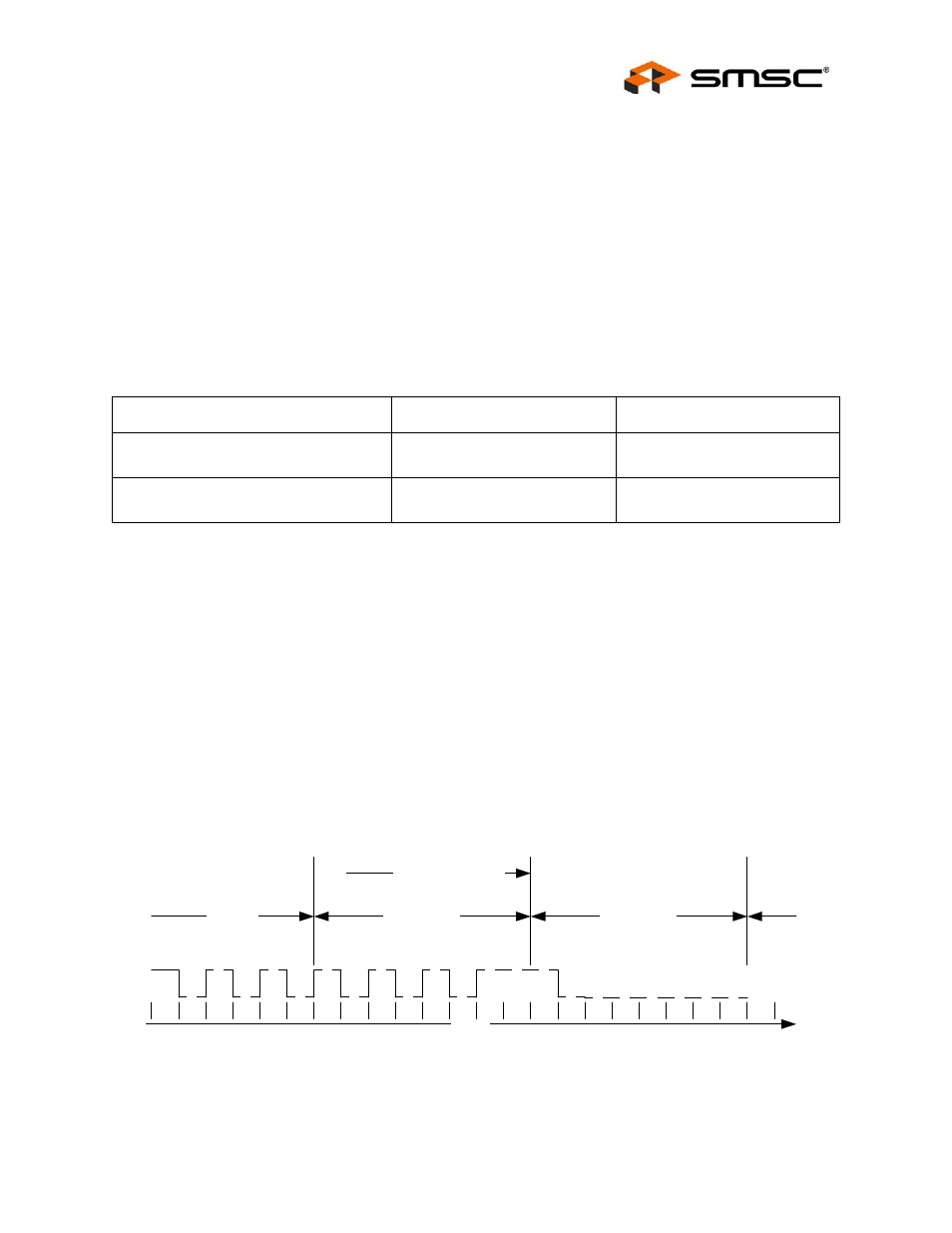

As defined by IEEE 1588, and shown in

, the message time stamp point is defined as the

leading edge of the first data bit following the Start of Frame Delimiter (SFD). However, since the

packet contents are not yet known, the time stamp can not yet be loaded into the capture register.

Therefore, the time stamp is first stored into a temporary internal holding register at the start of every

packet.

Table 11.1 IEEE 1588 Message Type Detection

IEEE 1588 CLOCK MODE

RECEIVE

TRANSMIT

Slave

(M_nS_x = 0)

Sync

Delay_Req

Master

(M_nS_x = 1)

Delay_Req

Sync

Figure 11.2 IEEE 1588 Message Time Stamp Point

bit time

0

1

0

1

0

1

0

1

0

1

0

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

Preamble

Octet

Ethernet

Start of Frame

Delimiter

First Octet

following

Start of Frame

Message Timestamp

Point