5 pio burst reads, Pio burst reads, Ncs or n – SMSC LAN9311i User Manual

Page 108: Datasheet 8.5.5 pio burst reads

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

Revision 1.4 (08-19-08)

108

SMSC LAN9311/LAN9311i

DATASHEET

8.5.5

PIO Burst Reads

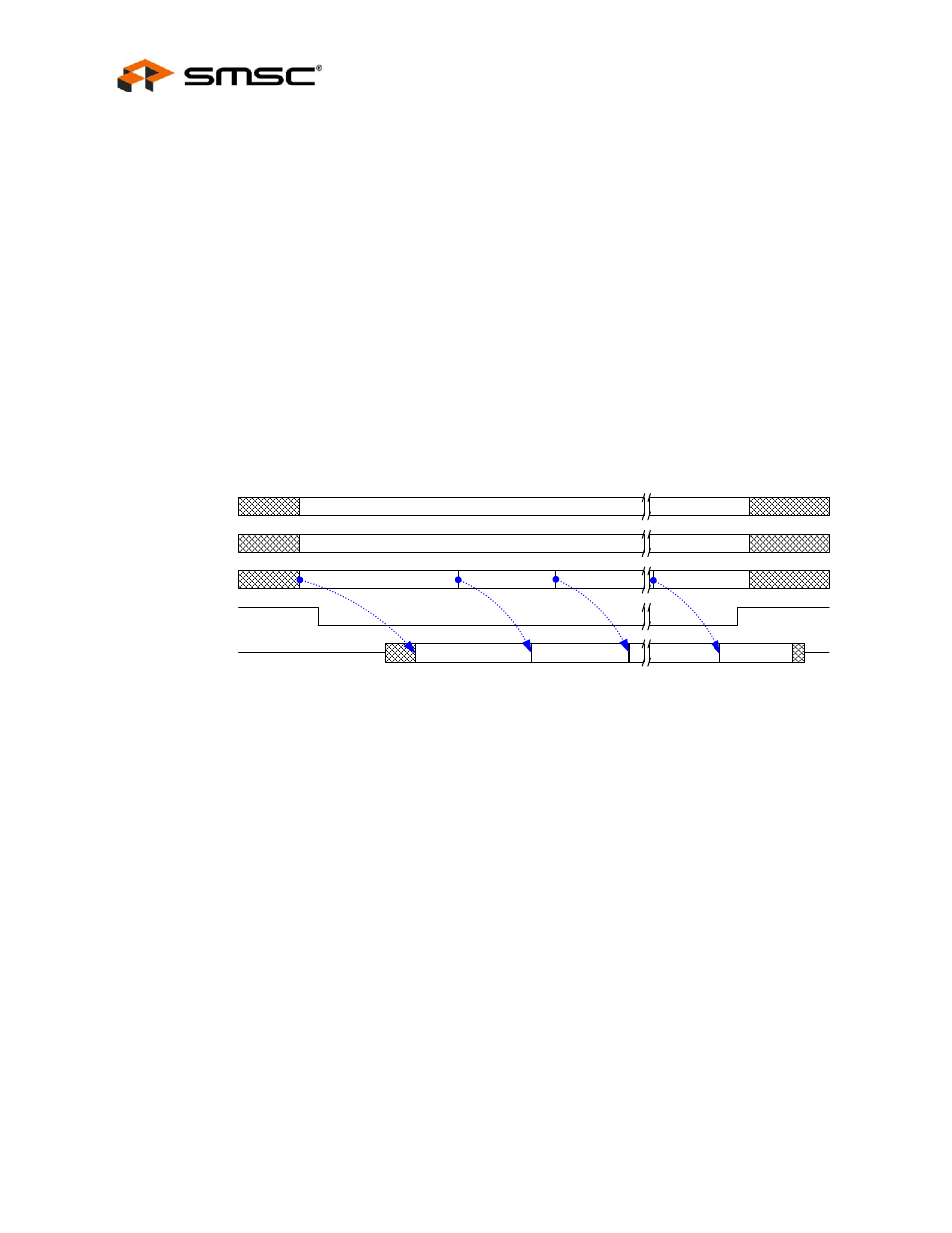

In this mode, performance is improved by allowing up to 16 WORD read cycles back-to-back. PIO

burst reads can be performed using Chip Select (nCS) or Read Enable (nRD). A PIO Burst Read

begins when both nCS and nRD are asserted. Either or both of these control signals must de-assert

between bursts for the period specified in

Table 15.9, “PIO Burst Read Cycle Timing Values,” on

. The burst cycle ends when either or both nCS and nRD are de-asserted. They may be

asserted and de-asserted in any order. Read data is valid as indicated in the functional timing diagram

in

.

Note:

A[1] must toggle during burst reads. Fresh data is supplied each time A[1] is toggled.

The endian select signal (END_SEL) has the same timing characteristics as the upper address lines.

Please refer to

Section 15.5.5, "PIO Burst Read Cycle Timing," on page 449

specifications for PIO burst read operations.

Note:

PIO burst reads are only supported for the RX Data FIFO. Burst reads from other registers are

not supported.

Figure 8.4 Functional Timing for PIO Burst Read Operation

END_SEL

A[x:5]

A[4:1]

nCS, nRD

D[15:0] (OUTPUT)

VALID

VALID

VALID

VALID

VALID

VALID

VALID

VALID

VALID

VALID