1 chip-level resets, 1 power-on reset (por), Chip-level resets – SMSC LAN9311i User Manual

Page 37: Power-on reset (por), Table 4.1, Summarize, Datasheet

Two Port 10/100 Managed Ethernet Switch with 16-Bit Non-PCI CPU Interface

Datasheet

SMSC LAN9311/LAN9311i

37

Revision 1.4 (08-19-08)

DATASHEET

Note 4.1

In the case of a soft reset, the EEPROM Loader is run, but loads only the MAC address

into the Host MAC. No other values are loaded by the EEPROM Loader in this case.

4.2.1

Chip-Level Resets

A chip-level reset event activates all internal resets, effectively resetting the entire LAN9311/LAN9311i.

Configuration straps are latched, and the EEPROM Loader is run as a result of chip-level resets. A

chip-level reset is initiated by assertion of any of the following input events:

Chip-level reset completion/configuration can be determined by polling the READY bit of the

Configuration Register (HW_CFG)

Power Management Control Register (PMT_CTRL)

until it is set.

When set, the READY bit indicates that the reset has completed and the device is ready to be

accessed.

With the exception of the

Hardware Configuration Register (HW_CFG)

Byte Order Test Register (BYTE_TEST)

, and

, read access to any internal resources is forbidden while the READY bit is cleared.

Writes to any address are invalid until the READY bit is set.

Note: The LAN9311/LAN9311i must be read at least once after any chip-level reset to ensure that

write operations function properly.

4.2.1.1

Power-On Reset (POR)

A power-on reset occurs whenever power is initially applied to the LAN9311/LAN9311i, or if the power

is removed and reapplied to the LAN9311/LAN9311i. This event resets all circuitry within the device.

Configuration straps are latched, and the EEPROM Loader is run as a result of this reset.

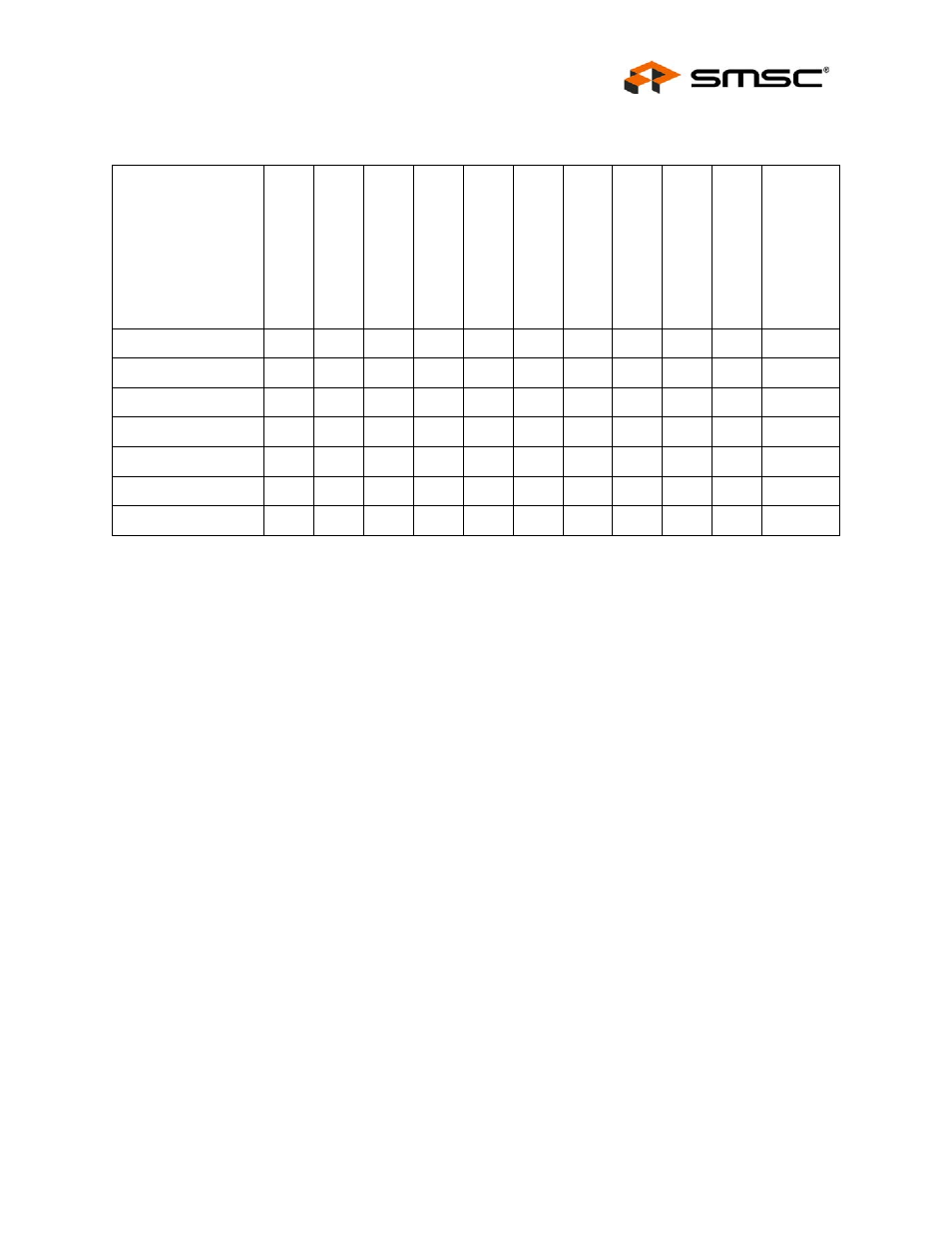

Table 4.1 Reset Sources and Affected LAN9311/LAN9311i Circuitry

RESET SOURCE

SYSTEM

CLOCKS/RESE

T/PM

E

SYS INTERRUPT

S

SWITCH FABRIC

ETHERNET PHYS

HB

I

HO

ST MA

C

EEPROM

C

O

NTROLLER

1

588

T

IME S

T

AMP

GPIO

/L

ED

C

O

NTROLLER

C

O

NFIG. S

T

RAP

S

LATCHED

EEPROM LOADER

RU

N

POR

X

X

X

X

X

X

X

X

X

X

X

nRST Pin

X

X

X

X

X

X

X

X

X

X

X

Digital Reset

X

X

X

X

X

X

X

X

X

Soft Reset

X

X

Port 2 PHY

X

Port 1 PHY

X

Virtual PHY

X