6 mac instruction execution times – Freescale Semiconductor ColdFire MCF52210 User Manual

Page 74

ColdFire Core

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

3-30

Freescale Semiconductor

3.3.5.6

MAC Instruction Execution Times

WDEBUG

—

5(2/0)

—

—

5(2/0)

—

—

—

1

The n is the number of registers moved by the MOVEM opcode.

2

If a MOVE.W #imm,SR instruction is executed and imm[13] equals 1, the execution time is 1(0/0).

3

The execution time for STOP is the time required until the processor begins sampling continuously for interrupts.

4

PEA execution times are the same for (d16,PC).

5

PEA execution times are the same for (d8,PC,Xn*SF).

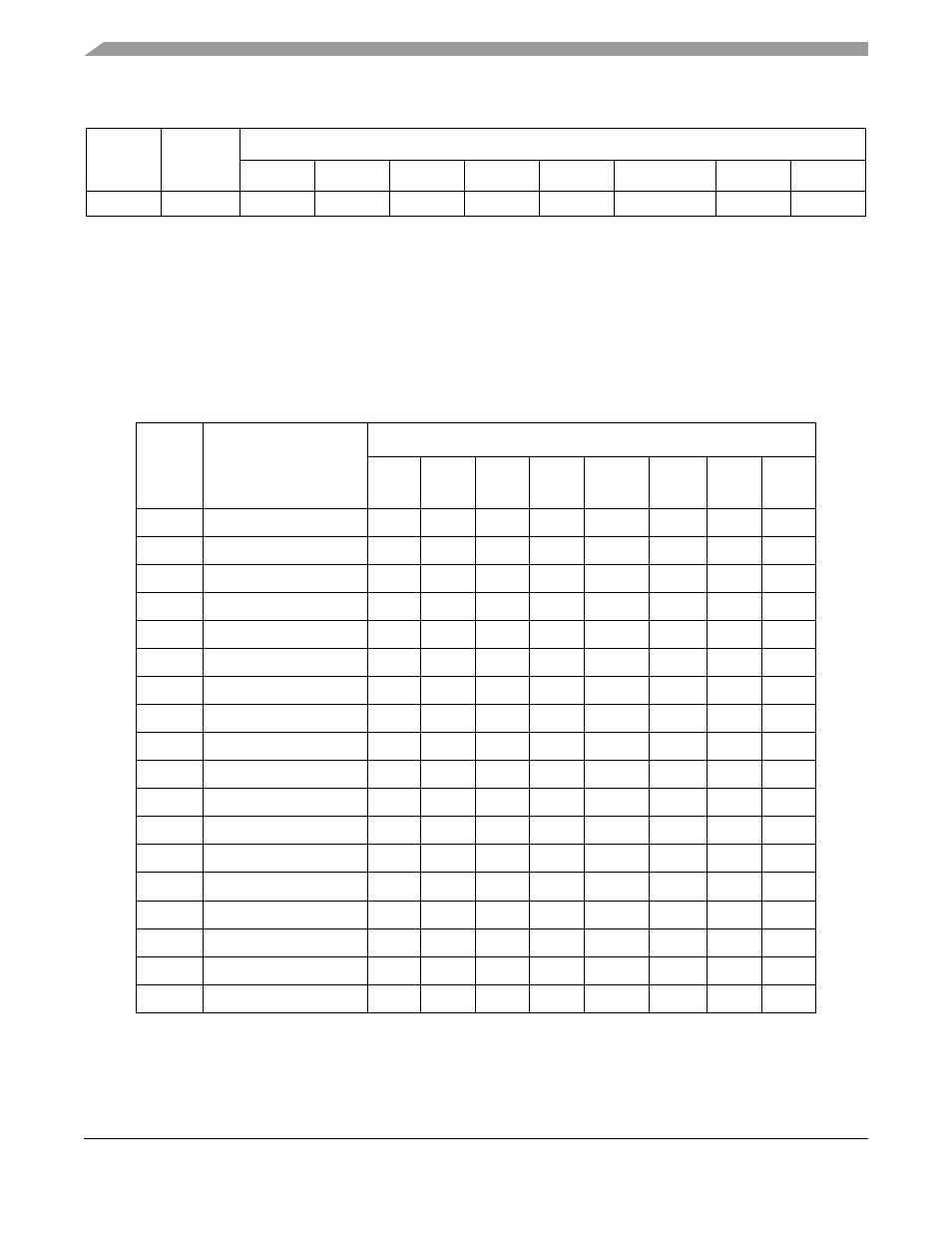

Table 3-17. MAC Instruction Execution Times

Opcode

Effective Address

Rn

(An)

(An)+

-(An)

(d16,An)

(d8,An,

Xn*SF)

xxx.wl

#xxx

MAC.L

Ry, Rx

3(0/0)

—

—

—

—

—

—

—

MAC.L

Ry, Rx,

—

4(1/0)

4(1/0)

4(1/0)

—

—

—

MAC.W

Ry, Rx

1(0/0)

—

—

—

—

—

—

—

MAC.W

Ry, Rx,

—

2(1/0)

2(1/0)

2(1/0)

2(1/0)

1

1

Effective address of (d16,PC) not supported

—

—

—

MOVE.L

1(0/0)

—

—

—

—

—

—

1(0/0)

MOVE.L

2(0/0)

—

—

—

—

—

—

2(0/0)

MOVE.L

1(0/0)

—

—

—

—

—

—

1(0/0)

MOVE.L

Racc,

1(0/0)

2

2

Storing the accumulator requires one additional processor clock cycle when rounding is performed

—

—

—

—

—

—

—

MOVE.L

MACSR,

1(0/0)

—

—

—

—

—

—

—

MOVE.L

Rmask,

1(0/0)

—

—

—

—

—

—

—

MSAC.L

Ry, Rx

3(0/0)

—

—

—

—

—

—

—

MSAC.W

Ry, Rx

1(0/0)

—

—

—

—

—

—

—

MSAC.L

Ry, Rx,

—

4(1/0)

4(1/0)

4(1/0)

—

—

—

MSAC.W

Ry, Rx,

—

2(1/0)

2(1/0)

2(1/0)

—

—

—

MULS.L

5(0/0)

7(1/0)

7(1/0)

7(1/0)

7(1/0)

—

—

—

MULS.W

3(0/0)

5(1/0)

5(1/0)

5(1/0)

5(1/0)

6(1/0)

5(1/0)

3(0/0)

MULU.L

5(0/0)

7(1/0)

7(1/0)

7(1/0)

7(1/0)

—

—

—

MULU.W

3(0/0)

5(1/0)

5(1/0)

5(1/0)

6(1/0)

5(1/0)

3(0/0)

Table 3-16. Miscellaneous Instruction Execution Times (continued)

Opcode

Effective Address

Rn

(An)

(An)+

-(An)

(d16,An)

(d8,An,Xn*SF)

xxx.wl

#xxx