Freescale Semiconductor ColdFire MCF52210 User Manual

Page 426

I

2

C Interface

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

25-6

Freescale Semiconductor

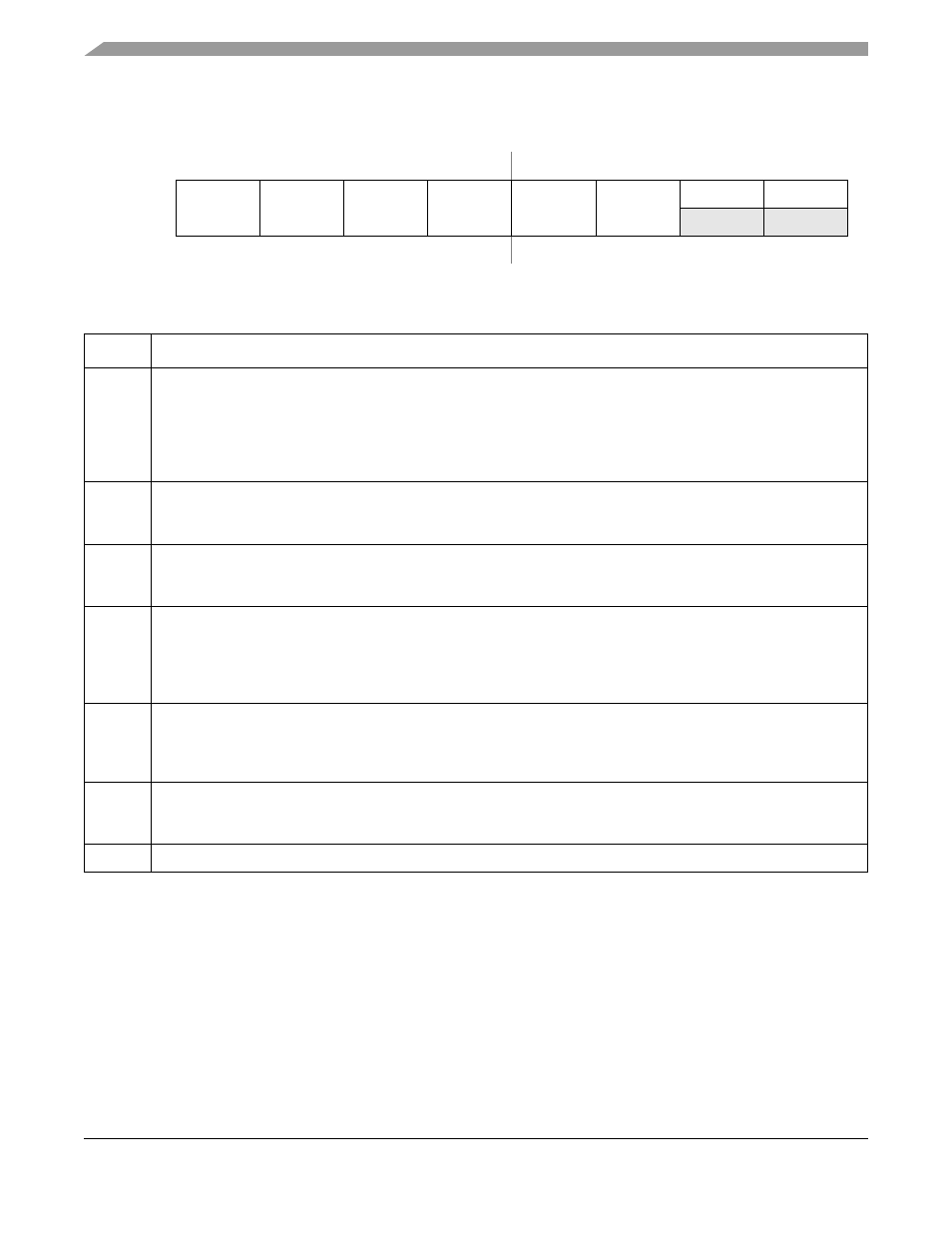

IPSBAR

Offset:

0x0308 (I2CR0)

0x0388 (I2CR1)

Access: User read/write

7

6

5

4

3

2

1

0

R

IEN

IIEN

MSTA

MTX

TXAK

RSTA

0

0

W

Reset:

0

0

0

0

0

0

0

0

Figure 25-4. I2CRn Registers

Table 25-4. I2CRn Field Descriptions

Field

Description

7

IEN

I

2

C enable. Controls the software reset of the entire I

2

C module. If the module is enabled in the middle of a byte

transfer, slave mode ignores the current bus transfer and starts operating when the next START condition is detected.

Master mode is not aware that the bus is busy; initiating a start cycle may corrupt the current bus cycle, ultimately

causing the current master or the I

2

C module to lose arbitration, after which bus operation returns to normal.

0 The I

2

C module is disabled, but registers can be accessed.

1 The I

2

C module is enabled. This bit must be set before any other I2CR bits have any effect.

6

IIEN

I

2

C interrupt enable.

0 I

2

C module interrupts are disabled, but currently pending interrupt condition is not cleared.

1 I

2

C module interrupts are enabled. An I

2

C interrupt occurs if I2SR[IIF] is also set.

5

MSTA

Master/slave mode select bit. If the master loses arbitration, MSTA is cleared without generating a STOP signal.

0 Slave mode. Changing MSTA from 1 to 0 generates a STOP and selects slave mode.

1 Master mode. Changing MSTA from 0 to 1 signals a START on the bus and selects master mode.

4

MTX

Transmit/receive mode select bit. Selects the direction of master and slave transfers.

0 Receive

1 Transmit. When the device is addressed as a slave, software must set MTX according to I2SR[SRW]. In master

mode, MTX must be set according to the type of transfer required. Therefore, when the MCU addresses a slave

device, MTX is always 1.

3

TXAK

Transmit acknowledge enable. Specifies the value driven onto SDA during acknowledge cycles for master and slave

receivers. Writing TXAK applies only when the I

2

C bus is a receiver.

0 An acknowledge signal is sent to the bus at the ninth clock bit after receiving one byte of data.

1 No acknowledge signal response is sent (acknowledge bit = 1).

2

RSTA

Repeat start. Always read as 0. Attempting a repeat start without bus mastership causes loss of arbitration.

0 No repeat start

1 Generates a repeated START condition.

1–0

Reserved, must be cleared.