3 peripheral revision register (rev), 4 peripheral additional info register (add_info) – Freescale Semiconductor ColdFire MCF52210 User Manual

Page 240

Universal Serial Bus, OTG Capable Controller

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

15-12

Freescale Semiconductor

15.4.1.3

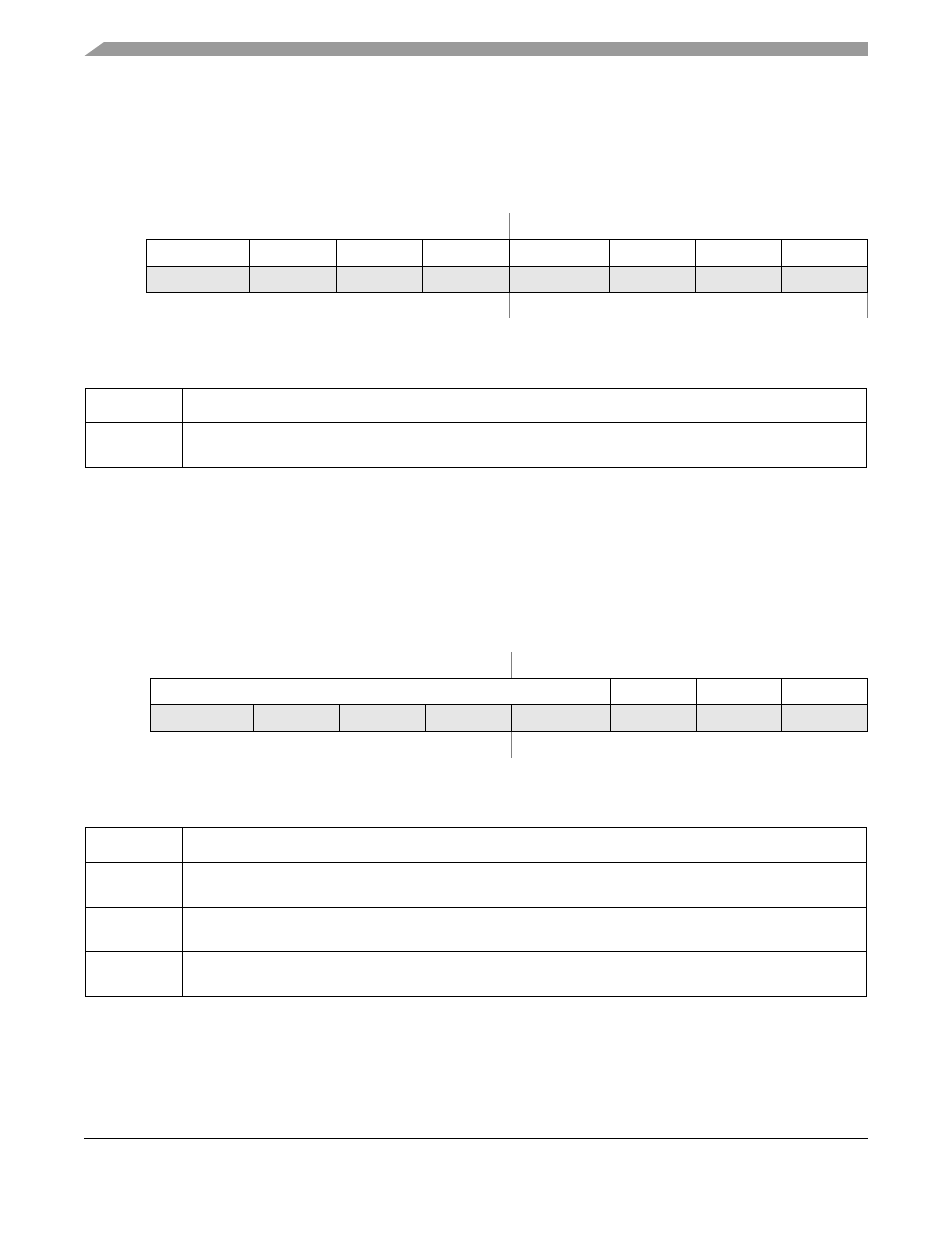

Peripheral Revision Register (REV)

This register contains the revision number of the USB Module.

shows the REV register.

15.4.1.4

Peripheral Additional Info Register (ADD_INFO)

The Peripheral Additional info Register reads back the value of the fixed Interrupt Request Level

(IRQ_NUM) along with the Host Enable bit. If set to 1, the Host Enable bit indicates the USB peripheral

is operating in host mode.

IPSBAR

Offset:

0x1C_0008 (REV)

Access: User read-only

7

6

5

4

3

2

1

0

R

REV7

REV6

REV5

REV4

REV3

REV2

REV1

REV0

W

Reset:

0

0

1

1

0

0

1

1

Figure 15-9. Peripheral Revision Register

Table 15-13. REV Field Descriptions

Field

Description

7–0

REVx

REV[7:0] indicate the revision number of the USB Core.

IPSBAR

Offset:

0x1C_000C (ADD_INFO)

Access: User read-only

7

6

5

4

3

2

1

0

R

IRQ_NUM

0

0

IEHOST

W

Reset:

0

0

0

0

0

0

0

1

Figure 15-10. Peripheral Additional Info Register

Table 15-14. ADD_INFO Field Descriptions

Field

Description

7–3

IRQ_NUM

Assigned Interrupt Request Number.

2–1

Reserved

RESERVED. These bits read back zeros.

0

IEHOST

This bit is set if host mode is enabled.