6 interrupt control registers (icrnx), 6 interrupt control registers (icrnx) -11, Table 14-10 – Freescale Semiconductor ColdFire MCF52210 User Manual

Page 221: 6 interrupt control registers (icr nx )

Interrupt Controller Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor

14-11

14.3.6

Interrupt Control Registers (ICRnx)

Each ICRnx, where x = 1, 2,..., 63, specifies the interrupt level (1–7) and the priority within the level (0–7).

As shown in

, all ICRnx registers can be read, but only ICRn8 through ICRn63 can be written.

Registers ICRn1 through ICRn7 are read-only because the interrupt levels for IRQ1 through IRQ7 are

hard-coded (see

Section 14.1.1, “Interrupt Controller Theory of Operation”

). The registers are described

.

It is the responsibility of the software to program the ICRnx registers with unique and non-overlapping

level and priority definitions. Failure to program the ICRnx registers in this manner can result in undefined

behavior. If a specific interrupt request is completely unused, the ICRnx value can remain in its reset (and

disabled) state.

Table 14-10. IACKLPRn Field Descriptions

Field

Description

7

Reserved

6–4

LEVEL

Interrupt level. Represents the interrupt level currently being acknowledged.

3–0

PRI

Interrupt Priority. Represents the priority within the interrupt level of the interrupt currently being acknowledged.

0 Priority 0

1 Priority 1

2 Priority 2

3 Priority 3

4 Priority 4

5 Priority 5

6 Priority 6

7 Priority 7

8 Mid-Point Priority associated with the fixed level interrupts only

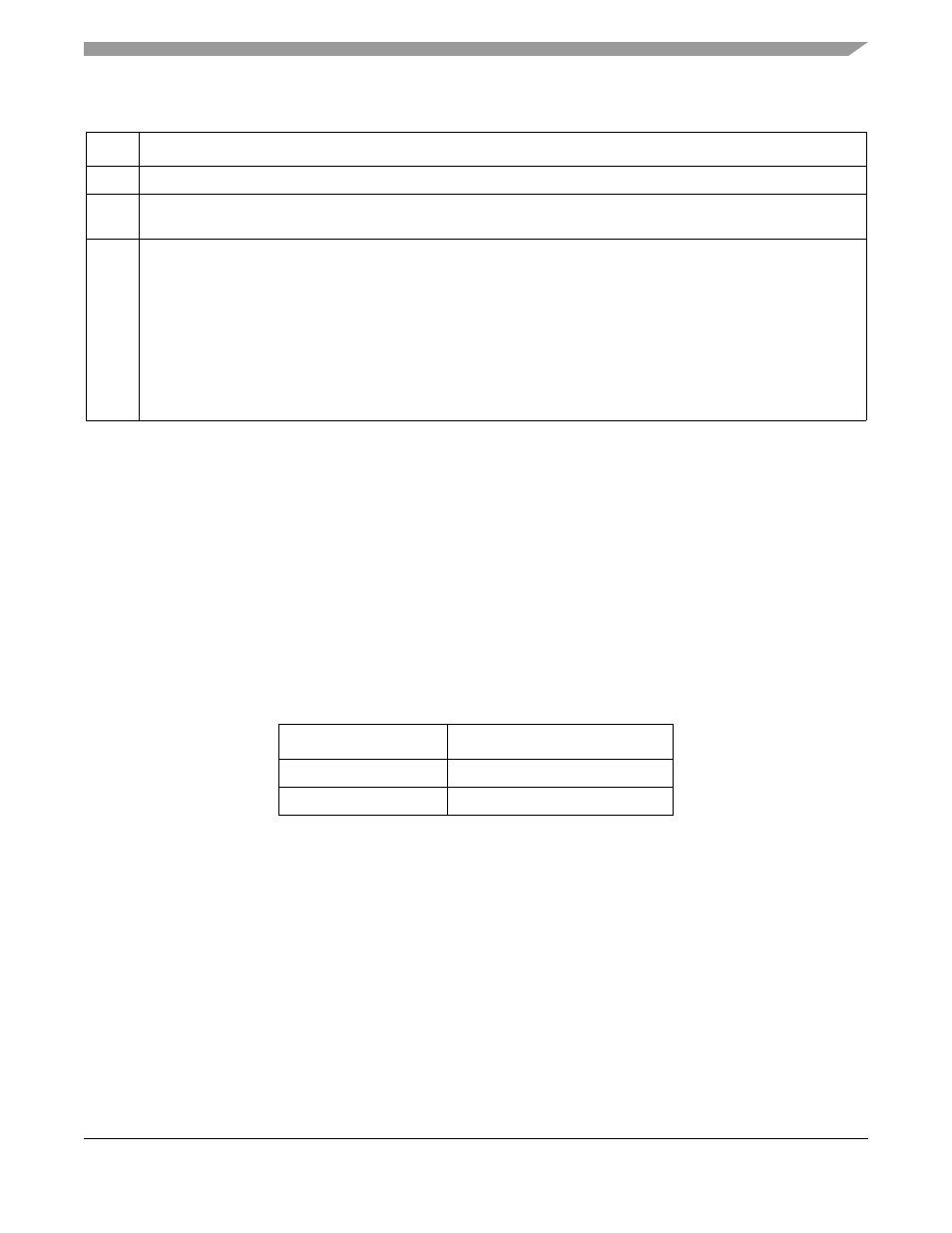

Table 14-11. ICRnx Register Accessibility

Registers

Access

ICRn1 – ICRn7

Read-only

ICRn8 – ICRn63

Read / write