4 memory map/register definitions, 4 memory map/register definitions -9 – Freescale Semiconductor ColdFire MCF52210 User Manual

Page 237

Universal Serial Bus, OTG Capable Controller

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor

15-9

because it is assumed that a second attempt will be queued and succeed in the future. For host mode, the

TOK_DNE interrupt fires and the TOK_PID field of the BDT is 1111 to indicate the DMA latency error.

Host mode software can decide to retry or move to another item in its schedule.

In the second case of oversized data packets the USB specification is very ambiguous. It assumes correct

software drivers on both sides. The overrun is not due to memory latency but due to a lack of space to put

the excess data. NAKing the packet may cause another retransmission of the already oversized packet data.

In response to oversized packets, the USB core continues ACKing the packet for non-isochronous

transfers. The data written to memory is clipped to the MaxPacket size so as not to corrupt system memory.

The core asserts the DMA_ERR bit of the ERR_STAT register (which could trigger an interrupt, as above)

and a TOK_DNE interrupt fires. The TOK_PID field of the BDT is not 1111 because the DMA_ERR is

not due to latency. The packet length field written back to the BDT is the MaxPacket value that represents

the length of the clipped data actually written to memory. The software can decide an appropriate course

of action from here for future transactions such as stalling the endpoint, canceling the transfer, disabling

the endpoint, etc.

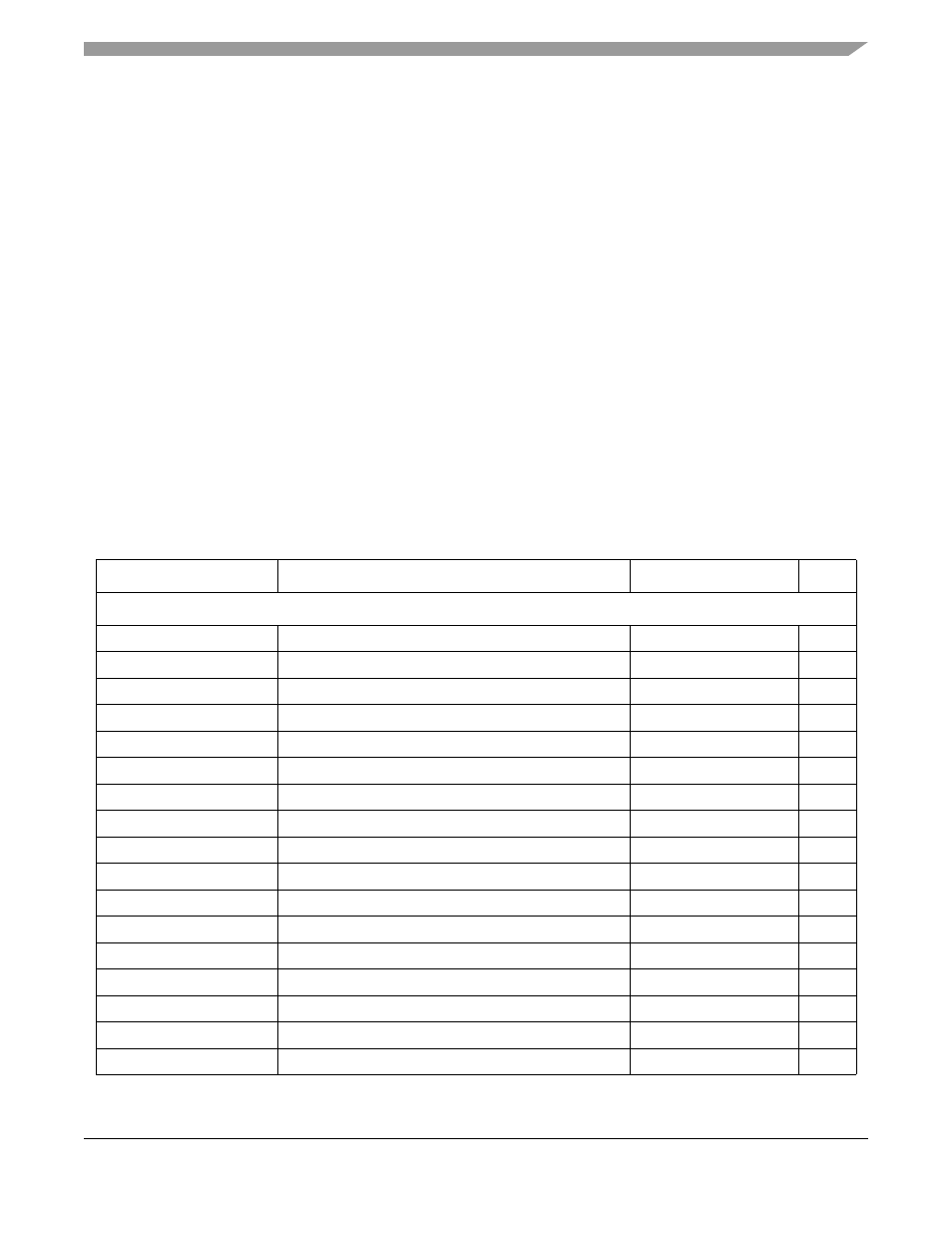

15.4

Memory Map/Register Definitions

This section provides the memory map and detailed descriptions of all USB interface registers. The

memory map of the USB interface is shown in

Table 15-4. USB Interface Memory Map

Address

Register

Acronym

Bits

USB OTG Registers

IPSBAR + 0x1C_0000

Peripheral ID Register

PER_ID

8

IPSBAR + 0x1C_0004

Peripheral ID Complement Register

ID_COMP

8

IPSBAR + 0x1C_0008

Peripheral Revision Register

REV

8

IPSBAR + 0x1C_000C

Peripheral Additional Info Register

ADD_INFO

8

IPSBAR + 0x1C_0010

OTG Interrupt Status Register

OTG_INT_STAT

8

IPSBAR + 0x1C_0014

OTG Interrupt Control Register

OTG_INT_EN

8

IPSBAR + 0x1C_0018

OTG Status Register

OTG_STATUS

8

IPSBAR + 0x1C_001C

OTG Control Register

OTG_CTRL

8

IPSBAR + 0x1C_0080

Interrupt Status Register

INT_STAT

8

IPSBAR + 0x1C_0084

Interrupt Enable Register

INT_ENB

8

IPSBAR + 0x1C_0088

Error Interrupt Status Register

ERR_STAT

8

IPSBAR + 0x1C_008C

Error Interrupt Enable Register

ERR_ENG

8

IPSBAR + 0x1C_0090

Status Register

STAT

8

IPSBAR + 0x1C_0094

Control Register

CTL

8

IPSBAR + 0x1C_0098

Address Register

ADDR

8

IPSBAR + 0x1C_009C

BDT Page Register 1

BDT_PAGE_01

8

IPSBAR + 0x1C_00A0

Frame Number Register Low

FRM_NUML

8