4 port clear output data registers (clrn), 4 port clear output data registers (clrn) -9, Table 13-4 – Freescale Semiconductor ColdFire MCF52210 User Manual

Page 203: 4 port clear output data registers (clr n )

General Purpose I/O Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor

13-9

13.6.4

Port Clear Output Data Registers (CLRn)

Writing 0s to a CLRn register clears the corresponding bits in the PORTn register. Writing 1s has no effect.

Reading the CLRn register returns 0s.

The CLRn registers with a full 8-bit implementation are shown in

. The remaining DDRn

registers use fewer than eight bits. Their bit definitions are shown in

,

. The fields are described in

, which applies to all CLRn

registers.

The CLRn registers are read/write.

Table 13-4. PORTnP/SETn Field Descriptions

Field

Description

PortnPx

Port nx pin data/set data bits.

1 PortnPx pin state is 1 (read); writing a 1 sets the corresponding port nx bit to 1

0 PortnPx pin state is 0

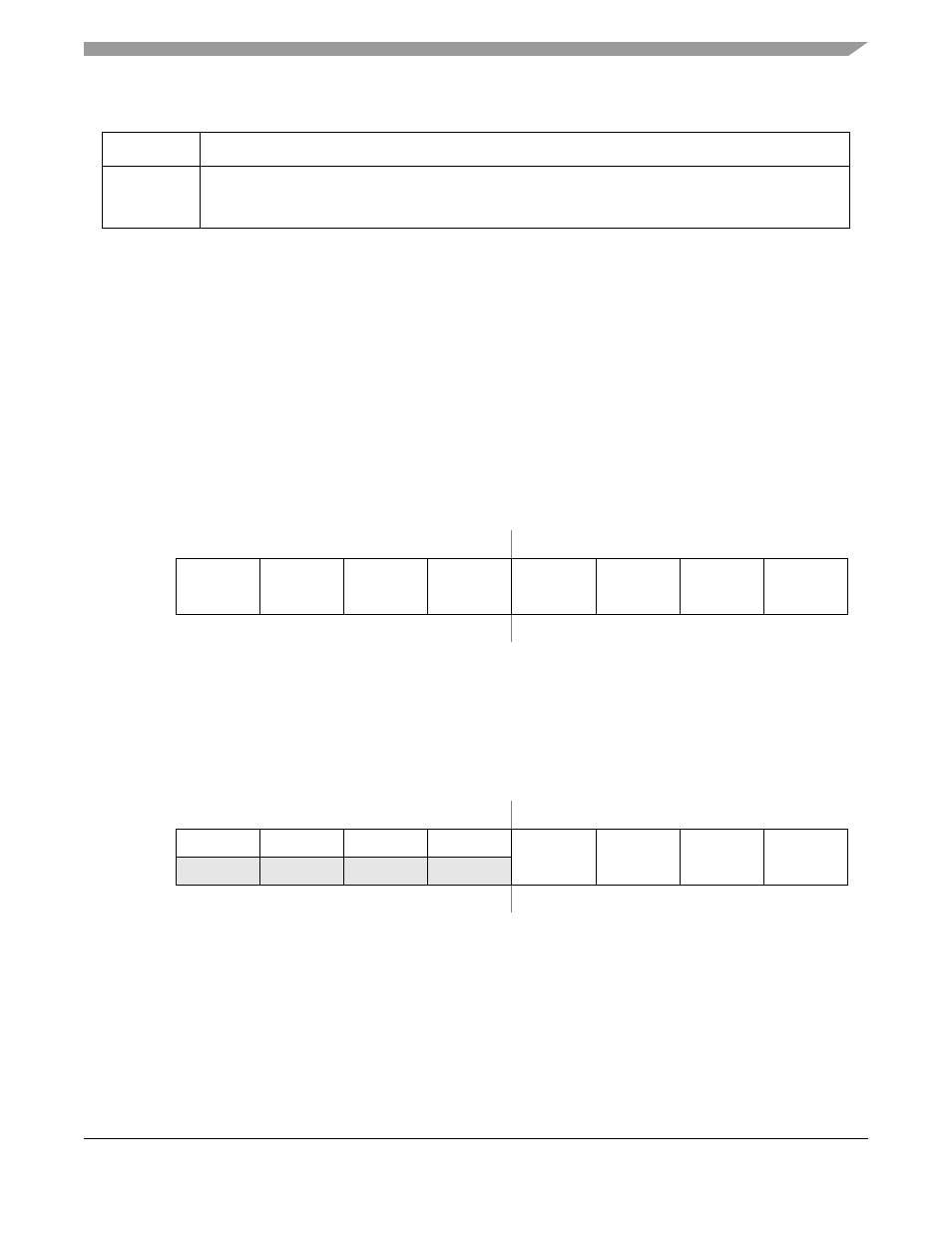

IPSBAR

Offsets:

0x10_005C (CLRDD)

0x10_0052 (CLRAN)

Access: User read/write

7

6

5

4

3

2

1

0

R

CLRn7

CLRn6

CLRn5

CLRn4

CLRn3

CLRn2

CLRn1

CLRn0

W

Reset:

0

0

0

0

0

0

0

0

Figure 13-17. Port Clear Output Data Registers with Bits 7:0 Implemented (CLRDD, CLRAN)

IPSBAR

Offsets:

0x10_0056 (CLRTA)

0x10_0057 (CLRTC)

0x10_0058 (CLRTD)

0x10_0059 (CLRUA)

0x10_005A (CLRUB)

0x10_005B (CLRUC)

Access: User read/write

7

6

5

4

3

2

1

0

R

0

0

0

0

CLRn3

CLRn2

CLRn1

CLRn0

W

Reset:

0

0

0

0

0

0

0

0

Figure 13-18. Port Clear Output Data Registers with Bits 3:0 Implemented (CLRTA, CLRTC, CLRTD, CLRUA,

CLRUB, CLRUC)