2 write a/d register – Freescale Semiconductor ColdFire MCF52210 User Manual

Page 523

Debug Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor

28-27

28.5.3.3.2

Write A/D Register (

WAREG

/

WDREG

)

The operand longword data is written to the specified address or data register. A write alters all 32 register

bits. A bus error response is returned if the CPU core is not halted.

Command Format:

Command Sequence:

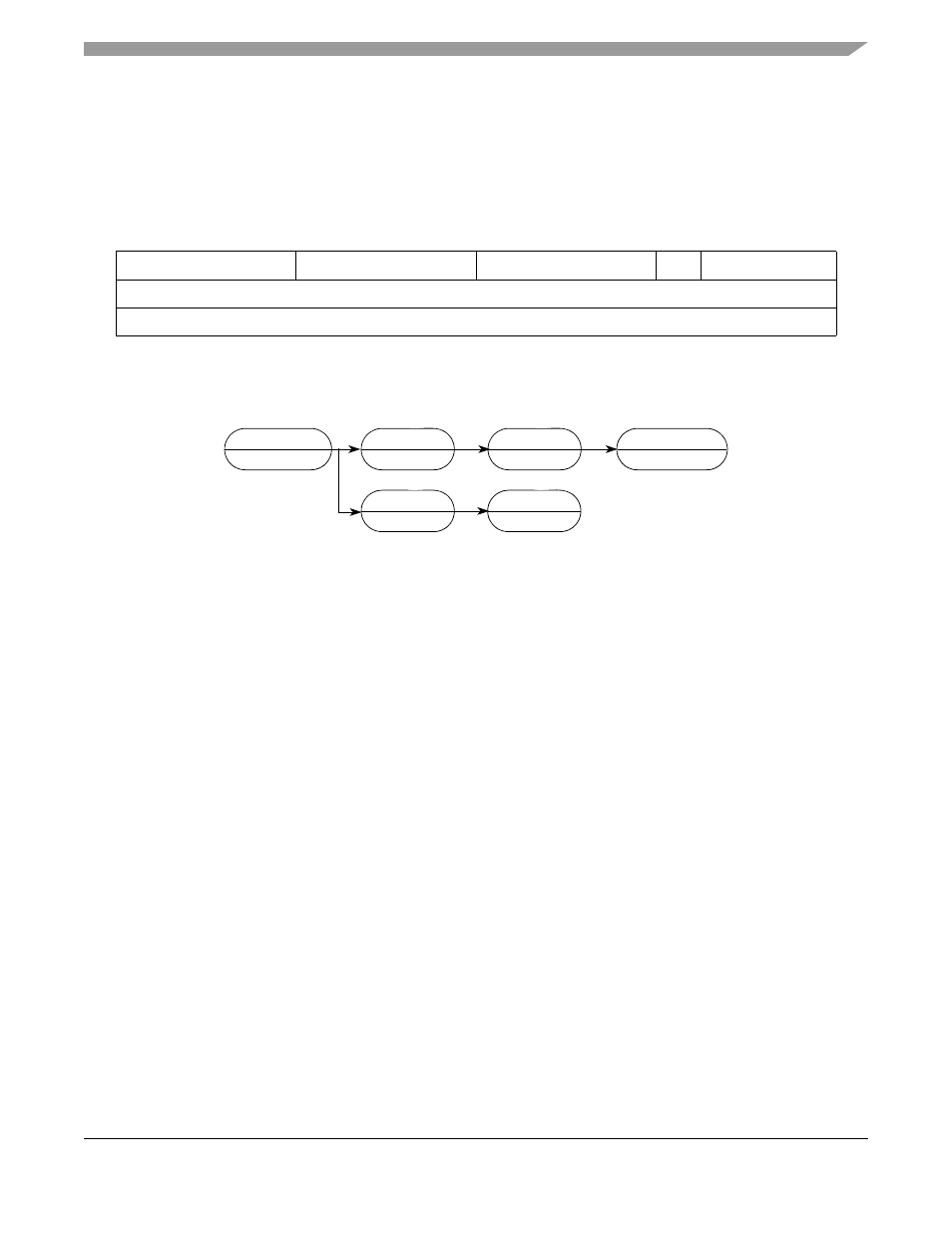

Figure 28-21.

WAREG

/

WDREG

Command Sequence

Operand Data:

Longword data is written into the specified address or data register. The data is

supplied most-significant word first.

Result Data:

Command complete status is indicated by returning 0xFFFF (with S cleared)

when the register write is complete.

28.5.3.3.3

Read Memory Location (

READ

)

Read data at the longword address. Address space is defined by BAAR[TT,TM]. Hardware forces

low-order address bits to 0s for word and longword accesses to ensure that word addresses are

word-aligned and longword addresses are longword-aligned.

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

0x2

0x0

0x8

A/D

Register

D[31:16]

D[15:0]

Figure 28-20.

WAREG

/

WDREG

Command Format

WAREG/WDREG

???

LS DATA

’NOT READY’

NEXT CMD

’NOT READY’

XXX

BERR

MS DATA

’NOT READY’

NEXT CMD

’CMD COMPLETE’