5 dma timer capture registers (dtcrn), 6 dma timer counters (dtcnn), 5 dma timer capture registers (dtcr n – Freescale Semiconductor ColdFire MCF52210 User Manual

Page 367: 6 dma timer counters (dtcn n, 5 dma timer capture registers (dtcr n ), 6 dma timer counters (dtcn n )

DMA Timers (DTIM0–DTIM3)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor

22-7

22.2.5

DMA Timer Capture Registers (DTCRn)

Each DTCRn latches the corresponding DTCNn value during a capture operation when an edge occurs on

DTINn, as programmed in DTMRn. The internal bus clock is assumed to be the clock source. DTINn

cannot simultaneously function as a clocking source and as an input capture pin. Indeterminate operation

results if DTINn is set as the clock source when the input capture mode is used.

22.2.6

DMA Timer Counters (DTCNn)

The current value of the 32-bit DTCNs can be read at anytime without affecting counting. Any write to

DTCNn clears it. The timer counter increments on the clock source rising edge (internal bus clock divided

by 1, internal bus clock divided by 16, or DTINn).

IPSBAR

Offset:

0x00_0404 (DTRR0)

0x00_0444 (DTRR1)

0x00_0484 (DTRR2)

0x00_04C4 (DTRR3)

Access: User read/write

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

R

REF (32-bit reference value)

W

Reset 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Figure 22-5. DTRRn Registers

Table 22-5. DTRRn Field Descriptions

Field

Description

31–0

REF

Reference value compared with the respective free-running timer counter (DTCNn) as part of the output-compare

function.

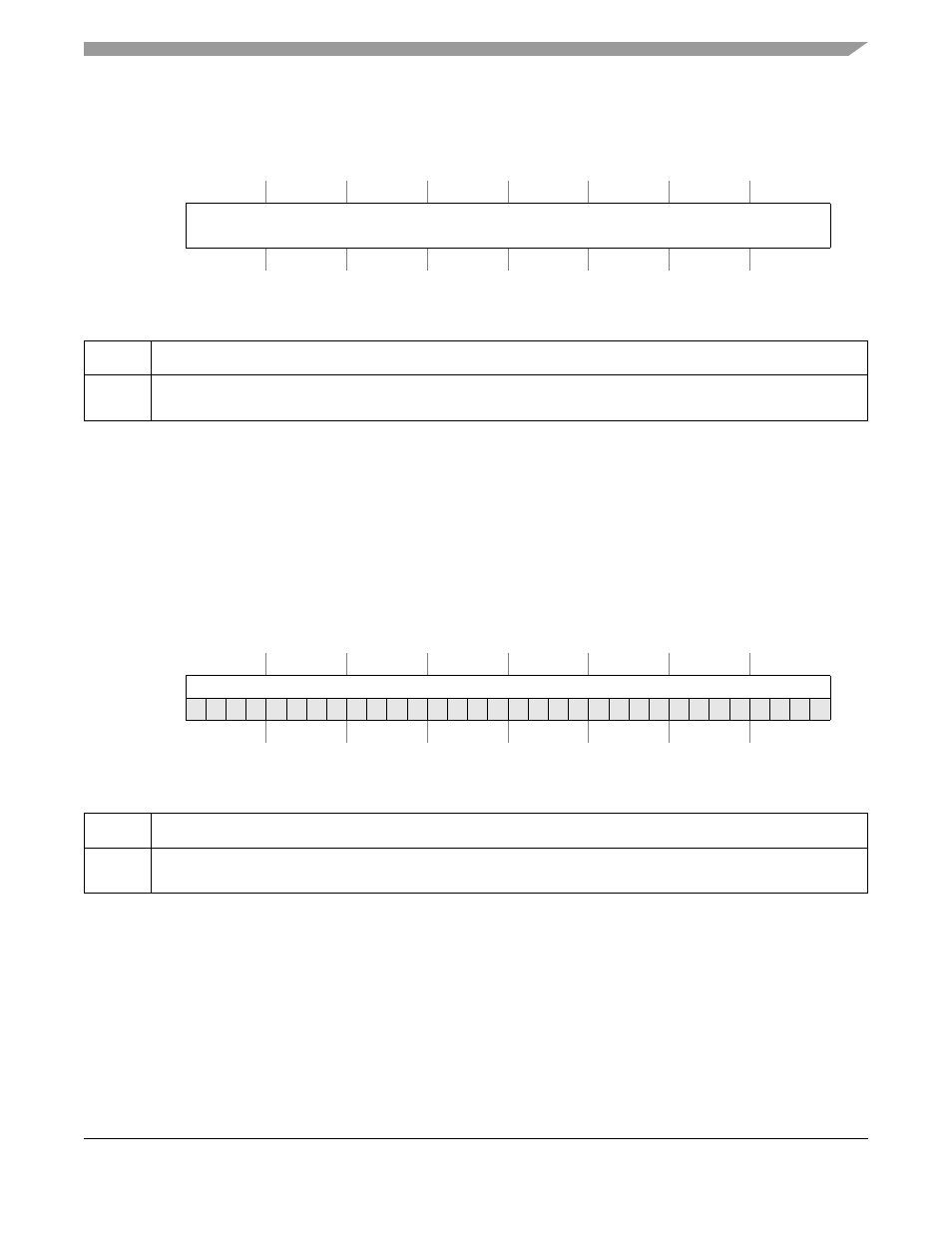

IPSBAR

Offset:

0x00_0408 (DTCR0)

0x00_0448 (DTCR1)

0x00_0488 (DTCR2)

0x00_04C8 (DTCR3)

Access: User read-only

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

R

CAP (32-bit capture counter value)

W

Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Figure 22-6. DTCRn Registers

Table 22-6. DTCRn Field Descriptions

Field

Description

31–0

CAP

Captures the corresponding DTCNn value during a capture operation when an edge occurs on DTIN

n

, as

programmed in DTMRn.