12 uart input port register (uipn), 11uart baud rate generator registers (ubg1 n, 12uart input port register (uip – Freescale Semiconductor ColdFire MCF52210 User Manual

Page 401: 12 uart input port register (uip n )

UART Modules

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor

24-15

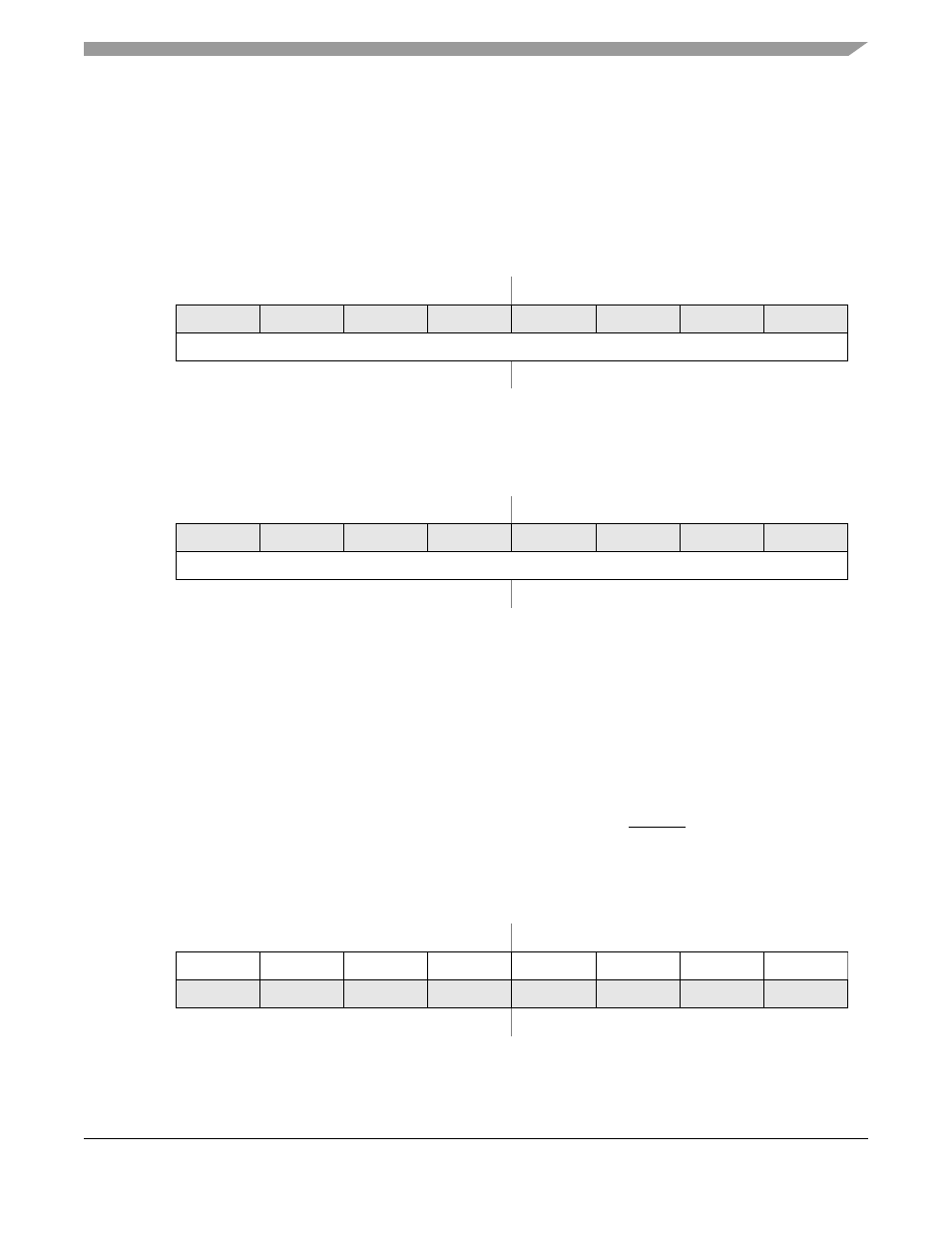

24.3.11 UART Baud Rate Generator Registers (UBG1n/UBG2n)

The UBG1n registers hold the MSB, and the UBG2n registers hold the LSB of the preload value. UBG1n

and UBG2n concatenate to provide a divider to the internal bus clock for transmitter/receiver operation,

as described in

Section 24.4.1.2.1, “Internal Bus Clock Baud Rates

NOTE

The minimum value loaded on the concatenation of UBG1n with UBG2n is

0x0002. The UBG2n reset value of 0x00 is invalid and must be written to

before the UART transmitter or receiver are enabled. UBG1n and UBG2n

are write-only and cannot be read by the CPU.

24.3.12 UART Input Port Register (UIPn)

The UIPn registers, shown in

, show the current state of the UCTSn input.

IPSBAR

Offset:

0x00_0218 (UBG10)

0x00_0258 (UBG11)

0x00_0298 (UBG12)

Access: User write-only

7

6

5

4

3

2

1

0

R

W

Divider MSB

Reset:

0

0

0

0

0

0

0

0

Figure 24-13. UART Baud Rate Generator Registers (UBG1n)

IPSBAR

Offset:

0x00_021C (UBG20)

0x00_025C (UBG21)

0x00_029C (UBG22)

Access: User write-only

7

6

5

4

3

2

1

0

R

W

Divider LSB

Reset:

0

0

0

0

0

0

0

0

Figure 24-14. UART Baud Rate Generator Registers (UBG2n)

IPSBAR

Offset:

0x00_0234 (UIP0)

0x00_0274 (UIP1)

0x00_02B4 (UIP2)

Access: User read-only

7

6

5

4

3

2

1

0

R

1

1

1

1

1

1

1

CTS

W

Reset:

1

1

1

1

1

1

1

1

Figure 24-15. UART Input Port Registers (UIPn)