Figure 18-3 – Freescale Semiconductor ColdFire MCF52210 User Manual

Page 295

ColdFire Flash Module (CFM)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor

18-5

NOTE

Flash accesses (reads/writes) by a bus master other than the core, DMA

controller, or writes to flash by the core during programming must use the

backdoor flash address of IPSBAR plus an offset of 0x0400_0000. For

example, for a DMA transfer from the first location of flash when IPSBAR

is at its default location of 0x4000_0000, the source register would be

loaded with 0x4400_0000. Backdoor access to flash for reads can be made

by the bus master, but it takes two cycles longer than a direct read of the

flash if using its FLASHBAR address.

NOTE

The flash is marked as valid on reset based on the RCON (reset

configuration) pin state. Flash space is valid on reset when booting in single

chip mode (RCON pin asserted and D[26]/D[17]/D[16] set to 110) or when

booting internally in master mode (RCON asserted and D[26]/D[17]/D[16]

are set to 111 and D[18] and D[19] are set to 00). See

for more details. When the default reset

configuration is not overridden, the MCU (by default) boots up in single

chip mode and the flash space is marked as valid at address 0x0. The flash

configuration field is checked during the reset sequence to see if the flash is

secured. If it is, the part always boots from internal flash because it is

marked as valid regardless of what is done for chip configuration.

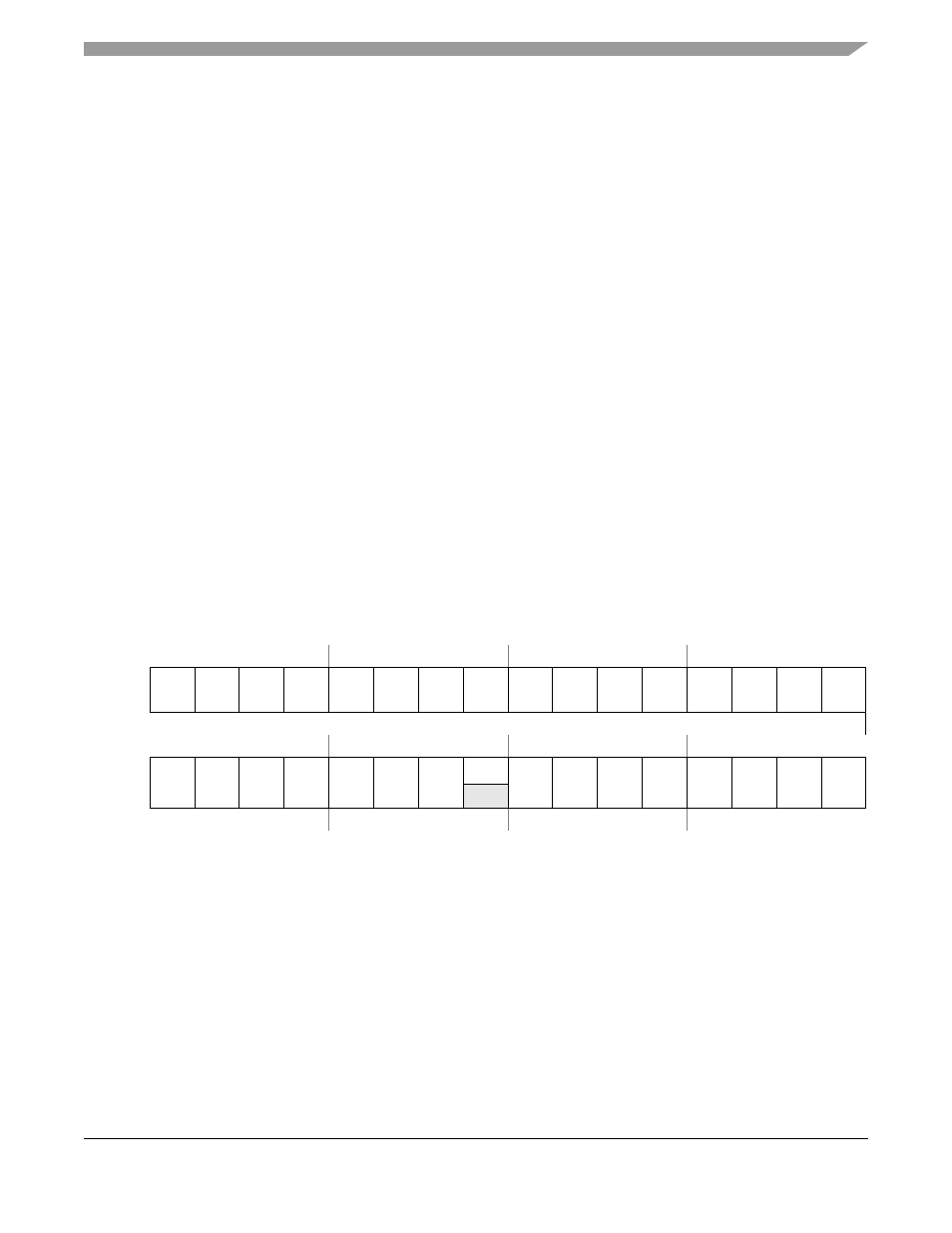

Address CPU + 0xC04 (FLASHBAR)

Access: User read/write

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

R

BA31 BA30 BA29 BA28 BA27 BA26 BA25 BA24 BA23 BA22 BA21 BA20 BA19

—

—

—

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

—

—

—

—

—

—

—

WP

1

1

The value of WP is determined at power-on reset.

—

—

C/I

SC

SD

UC

UD

V

2

2

The reset value for the valid bit is determined by the chip mode selected at reset (see

Chapter 9, “Chip Configuration Module

”).

W

Reset

0

0

0

0

0

0

0

0

0

1

0

0

0

0

0

Figure 18-3. Flash Base Address Register (FLASHBAR)