Table 28-22, For re, Command sequence – Freescale Semiconductor ColdFire MCF52210 User Manual

Page 532

Debug Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

28-36

Freescale Semiconductor

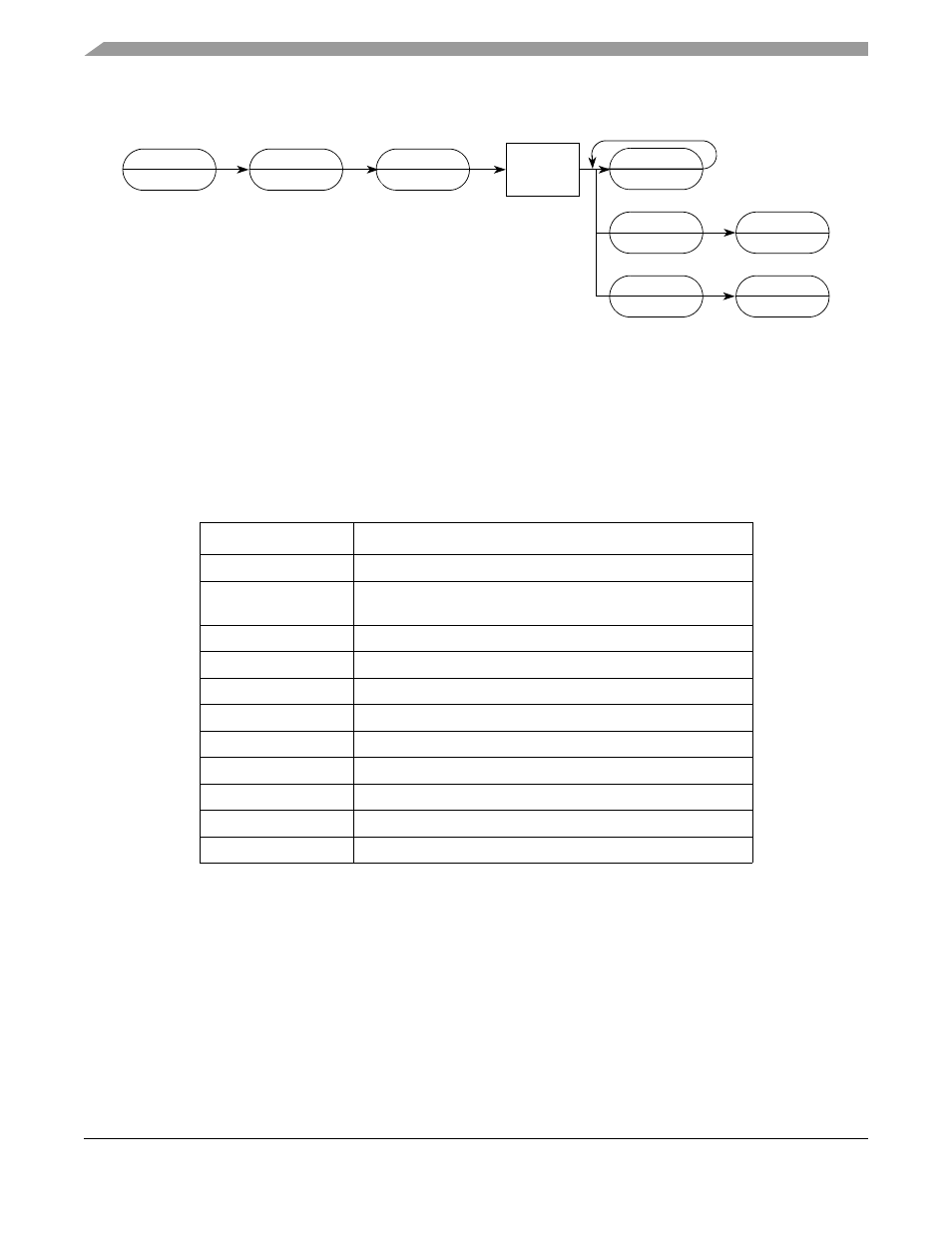

Command Sequence:

Figure 28-37.

RCREG

Command Sequence

Operand Data:

The only operand is the 32-bit Rc control register select field.

Result Data:

Control register contents are returned as a longword, most-significant word first.

The implemented portion of registers smaller than 32 bits is guaranteed correct;

other bits are undefined.

Rc encoding: See

.

28.5.3.3.11

BDM Accesses of the Stack Pointer Registers (A7: SSP and USP)

The ColdFire core supports two unique stack pointer (A7) registers: the supervisor stack pointer (SSP) and

the user stack pointer (USP). The hardware implementation of these two programmable-visible 32-bit

registers does not uniquely identify one as the SSP and the other as the USP. Rather, the hardware uses one

32-bit register as the currently-active A7; the other is named the OTHER_A7. Therefore, the contents of

the two hardware registers is a function of the operating mode of the processor:

if SR[S] = 1

then

A7 = Supervisor Stack Pointer

OTHER_A7 = User Stack Pointer

Table 28-22. Control Register Map

Rc

Register Definition

0x(0,1)80–0x(0,1)87

Data Registers 0–7 (0 = load, 1 = store)

0x(0,1)88–0x(0,1)8F

Address Registers 0–7 (0 = load, 1 = store)

(A7 is user stack pointer)

0x800

Other Stack Pointer (OTHER_A7)

0x801

Vector Base Register (VBR)

0x804

MAC Status Register (MACSR)

0x805

MAC Mask Register (MASK)

0x806

MAC Accumulator (ACC)

0x80E

Status Register (SR)

0x80F

Program Register (PC)

0xC04

Flash Base Address Register (FLASHBAR)

0xC05

RAM Base Address Register (RAMBAR)

XXX

’NOT READY’

RCREG

???

MS ADDR

’NOT READY’

MS ADDR

’NOT READY’

NEXT CMD

’NOT READY’

READ

CONTROL

REGISTER

XXX

BERR

NEXT CMD

MS RESULT

NEXT CMD

LS RESULT