Freescale Semiconductor ColdFire MCF52210 User Manual

Page 390

UART Modules

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

24-4

Freescale Semiconductor

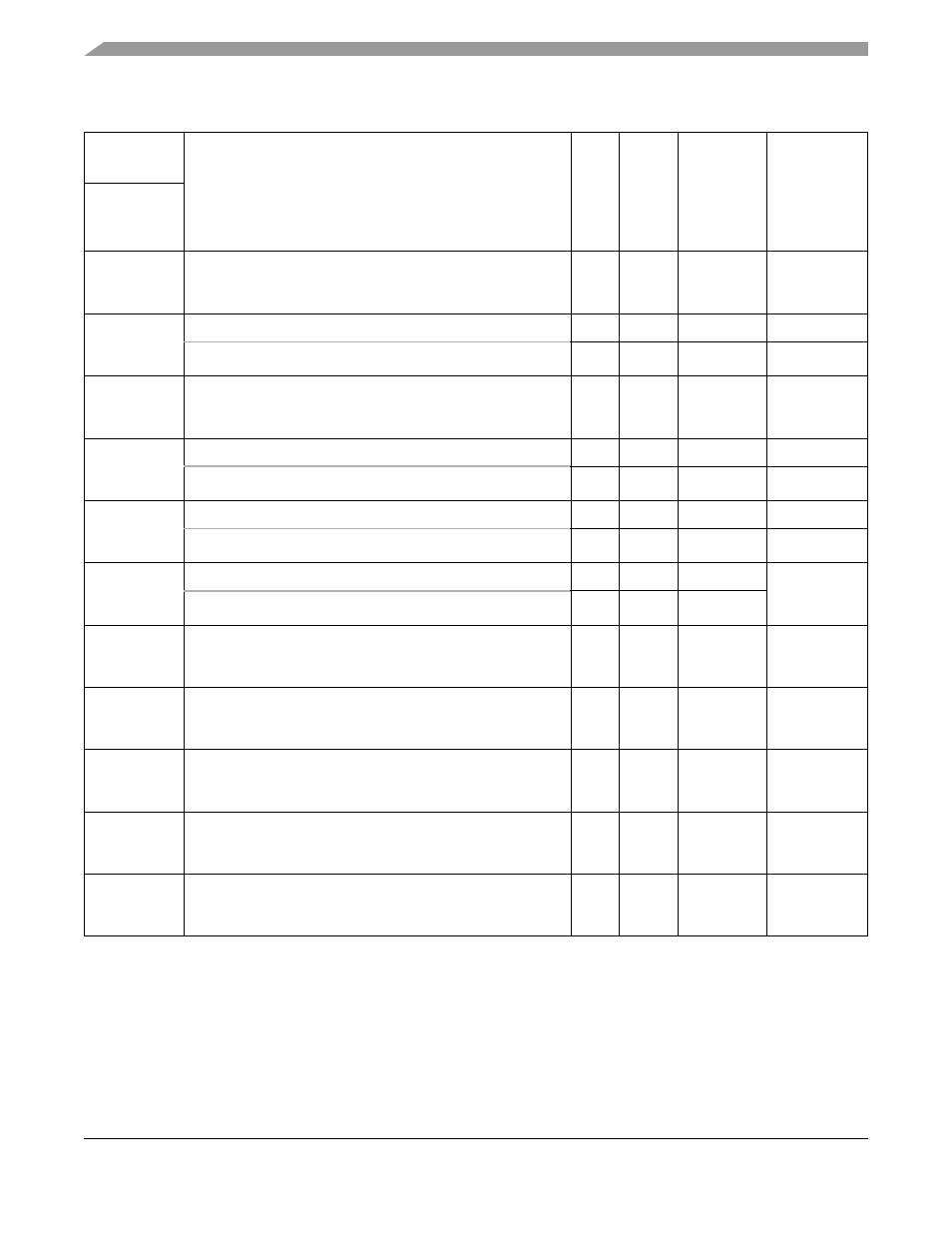

Table 24-2. UART Module Memory Map

IPSBAR

Offset

Register

Width

(bit)

Access Reset Value Section/Page

UART0

UART1

UART2

0x00_0200

0x00_0240

0x00_0280

UART Mode Registers

1

(UMR1n), (UMR2n)

1

UMR1n, UMR2n, and UCSRn must be changed only after the receiver/transmitter is issued a software reset command. If

operation is not disabled, undesirable results may occur.

8

R/W

0x00

0x00_0204

0x00_0244

0x00_0284

UART Status Register (USRn)

8

R

0x00

UART Clock Select Register

(UCSRn) 8

W

Section

0x00_0208

0x00_0248

0x00_0288

UART Command Registers (UCRn)

8

W

0x00

0x00_020C

0x00_024C

0x00_028C

UART Receive Buffers (URBn)

8

R

0xFF

UART Transmit Buffers (UTBn)

8

W

0x00

0x00_0210

0x00_0250

0x00_0290

UART Input Port Change Register (UIPCRn)

8

R

See Section

UART Auxiliary Control Register (UACRn)

8

W

0x00

0x00_0214

0x00_0254

0x00_0294

UART Interrupt Status Register (UISRn)

8

R

0x00

UART Interrupt Mask Register (UIMRn)

8

W

0x00

0x00_0218

0x00_0258

0x00_0298

UART Baud Rate Generator Register (UBG1n)

8

W

2

2

Reading this register results in undesired effects and possible incorrect transmission or reception of characters. Register

contents may also be changed.

0x00

0x00_021C

0x00_025C

0x00_029C

UART Baud Rate Generator Register (UBG2n)

8

0x00

0x00_0234

0x00_0274

0x00_02B4

UART Input Port Register (UIPn)

8

R

0xFF

0x00_0238

0x00_0278

0x00_02B8

UART Output Port Bit Set Command Register (UOP1n)

8

0x00

0x00_023C

0x00_027C

0x00_02BC

UART Output Port Bit Reset Command Register (UOP0n)

8

0x00