6 status register (adstat), 6 status register (adstat) -11 – Freescale Semiconductor ColdFire MCF52210 User Manual

Page 447

Analog-to-Digital Converter (ADC)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor

26-11

26.4.6

Status Register (ADSTAT)

This register provides the current status of the ADC module. RDYn bits are cleared by reading their

corresponding result (ADRSLTn) registers. The HLMTI and LLMTI bits are cleared by writing 1 to each

asserted bit in the ADC limit status (ADLSTAT) register. Likewise, the ZCI bit is cleared by writing 1 to

each asserted bit in the ADC zero crossing status (ADZCSTAT) register. The EOSIn bits are cleared by

writing 1 to them.

Except for CIP0 and CIP1 all bits in ADSTAT are sticky – after being set, they require some specific action

to be cleared. They are not cleared automatically on the next scan sequence.

IPSBAR

Offset: 0x19_000A (ADSDIS)

Access: read/write

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R

0

0

0

0

0

0

0

0

DS7

DS6

DS5

DS4

DS3

DS2

DS1

DS0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Figure 26-8. Sample Disable Register (ADSDIS)

Table 26-10. ADSDIS Field Descriptions

Field

Description

15–8

Reserved, should be cleared.

7–0

DSn

Disable Sample bits. Setting or clearing DSn enables or disables the corresponding SAMPLEn field.

0 Enable SAMPLEn

1 Disable SAMPLEn and all subsequent samples. Which samples are actually disabled depends on the

conversion mode, sequential/parallel, and the value of SIMULT.

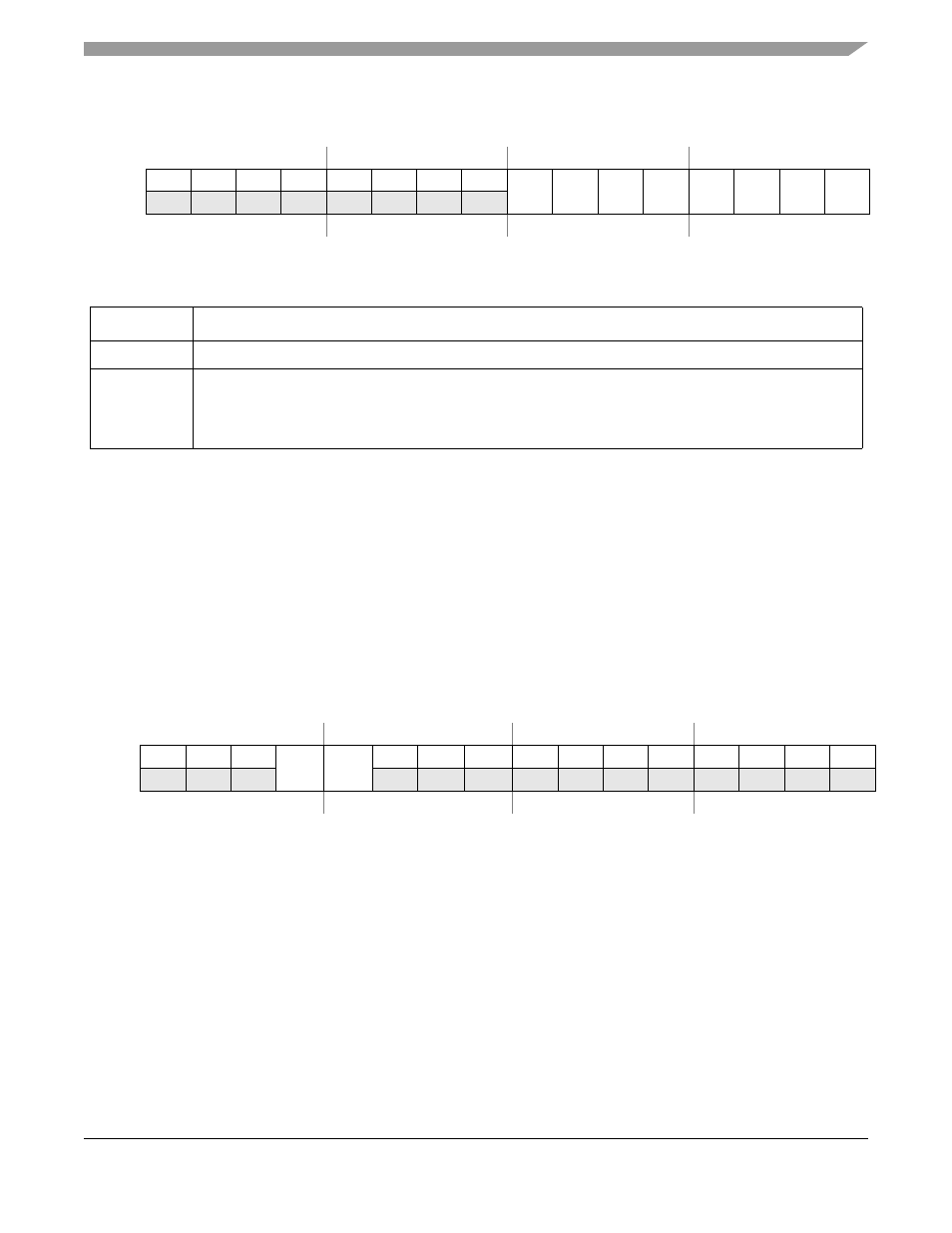

IPSBAR

Offset: 0x19_000C (ADSTAT)

Access: read/write

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

R CIP0

CIP1

0

EOSI1 EOSI0

ZCI

LLMTI HLMTI RDY7 RDY6 RDY5 RDY4 RDY3 RDY2 RDY1 RDY0

W

Reset

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Figure 26-9. Status Register (ADSTAT)