1 pwm enable register (pwme), 1 pwm enable register (pwme) -3 – Freescale Semiconductor ColdFire MCF52210 User Manual

Page 477

Pulse-Width Modulation (PWM) Module

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor

27-3

27.2.1

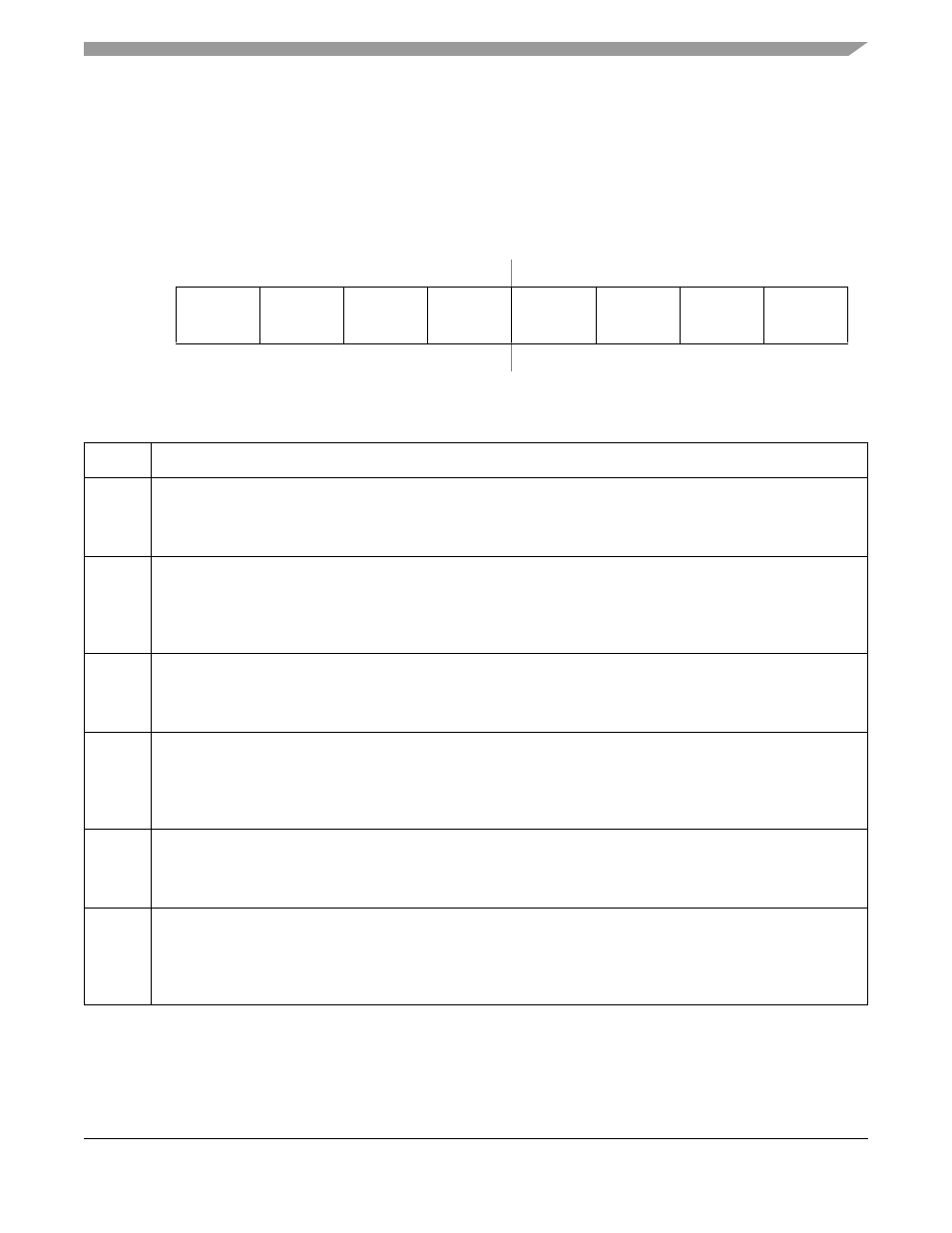

PWM Enable Register (PWME)

Each PWM channel has an enable bit (PWMEn) to start its waveform output. While in run mode, if all

eight PWM output channels are disabled (PWME[7:0] = 0), the prescaler counter shuts off for power

savings. See

Section 27.3.2.1, “PWM Enable”

for more information.

IPSBAR

Offset:

0x1B_0000 (PWME)

Access: User Read/Write

7

6

5

4

3

2

1

0

R

PWME7

PWME6

PWME5

PWME4

PWME3

PWME2

PWME1

PWME0

W

Reset:

0

0

0

0

0

0

0

0

Figure 27-2. PWM Enable Register (PWME)

Table 27-2. PWME Field Descriptions

Field

Description

7

PWME5

PWM Channel 7 Output Enable. If enabled, the PWM signal becomes available at PWMOUT7 when its

corresponding clock source begins its next cycle.

0 PWM output disabled

1 PWM output enabled

6

PWME6

PWM Channel 6 Output Enable. If enabled, the PWM signal becomes available at PWMOUT6 when its

corresponding clock source begins its next cycle. If PWMCTL[CON67] is set, then this bit has no effect and

PWMOUT6 is disabled.

0 PWM output disabled

1 PWM output enabled

5

PWME5

PWM Channel 5 Output Enable. If enabled, the PWM signal becomes available at PWMOUT5 when its

corresponding clock source begins its next cycle.

0 PWM output disabled

1 PWM output enabled

4

PWME4

PWM Channel 4 Output Enable. If enabled, the PWM signal becomes available at PWMOUT4 when its

corresponding clock source begins its next cycle. If PWMCTL[CON45] is set, then this bit has no effect and

PWMOUT4 is disabled.

0 PWM output disabled

1 PWM output enabled

3

PWME3

PWM Channel 3 Output Enable. If enabled, the PWM signal becomes available at PWMOUT3 when its

corresponding clock source begins its next cycle.

0 PWM output disabled

1 PWM output enabled

2

PWME2

PWM Channel 2 Output Enable. If enabled, the PWM signal becomes available at PWMOUT2 when its

corresponding clock source begins its next cycle. If PWMCTL[CON23] is set, then this bit has no effect and

PWMOUT2 is disabled.

0 PWM output disabled

1 PWM output enabled, if PWMCTL[CON23]=0