7 uart transmit buffers (utbn), 8 uart input port change registers (uipcrn), 7 uart transmit buffers (utb – Freescale Semiconductor ColdFire MCF52210 User Manual

Page 398: 8 uart input port change registers (uipcr, 7 uart transmit buffers (utb n ), 8 uart input port change registers (uipcr n )

UART Modules

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

24-12

Freescale Semiconductor

24.3.7

UART Transmit Buffers (UTBn)

The transmit buffers consist of the transmitter holding register and the transmitter shift register. The

holding register accepts characters from the bus master if UART’s USRn[TXRDY] is set. A write to the

transmit buffer clears USRn[TXRDY], inhibiting any more characters until the shift register can accept

more data. When the shift register is empty, it checks if the holding register has a valid character to be sent

(TXRDY = 0). If there is a valid character, the shift register loads it and sets USRn[TXRDY] again. Writes

to the transmit buffer when the UART’s TXRDY is cleared and the transmitter is disabled have no effect

on the transmit buffer.

shows UTBn. TB contains the character in the transmit buffer.

24.3.8

UART Input Port Change Registers (UIPCRn)

, hold the current state and the change-of-state for UCTSn.

IPSBAR

Offset:

0x00_020C (URB0)

0x00_024C (URB1)

0x00_028C (URB2)

Access: User read-only

7

6

5

4

3

2

1

0

R

RB

W

Reset:

1

1

1

1

1

1

1

1

Figure 24-8. UART Receive Buffer (URBn)

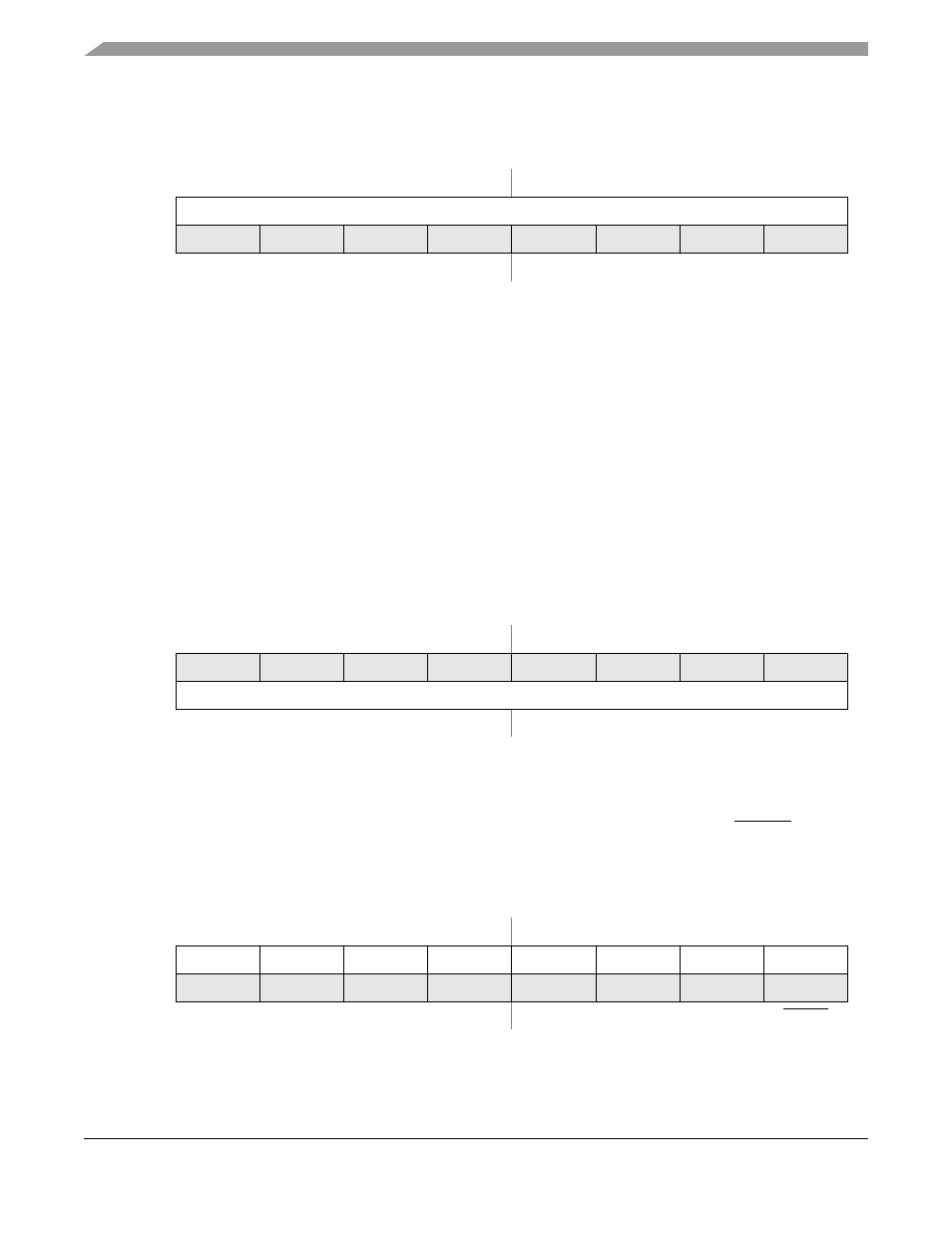

IPSBAR

Offset:

0x00_020C (UTB0)

0x00_024C (UTB1)

0x00_028C (UTB2)

Access: User write-only

7

6

5

4

3

2

1

0

R

W

TB

Reset:

0

0

0

0

0

0

0

0

Figure 24-9. UART Transmit Buffer (UTBn)

IPSBAR

Offset:

0x00_0210 (UIPCR0)

0x00_0250 (UIPCR1)

0x00_0290 (UIPCR2)

Access: User read-only

7

6

5

4

3

2

1

0

R

0

0

0

COS

1

1

1

CTS

W

Reset:

0

0

0

0

1

1

1

UCTSn

Figure 24-10. UART Input Port Changed Registers (UIPCRn)