2 memory map/register definition, 2 memory map/register definition -2, Table 20-1 – Freescale Semiconductor ColdFire MCF52210 User Manual

Page 332

Programmable Interrupt Timers (PIT0–PIT1)

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

20-2

Freescale Semiconductor

NOTE

The low-power interrupt control register (LPICR) in the system control

module specifies the interrupt level at or above which the device can be

brought out of a low-power mode.

In wait mode, the PIT module continues to operate as in run mode and can be configured to exit the

low-power mode by generating an interrupt request. In doze mode with the PCSRn[DOZE] bit set, PIT

module operation stops. In doze mode with the PCSRn[DOZE] bit cleared, doze mode does not affect PIT

operation. When doze mode is exited, PIT continues operating in the state it was in prior to doze mode. In

stop mode, the internal bus clock is absent and PIT module operation stops.

In debug mode with the PCSRn[DBG] bit set, PIT module operation stops. In debug mode with the

PCSRn[DBG] bit cleared, debug mode does not affect PIT operation. When debug mode is exited, the PIT

continues to operate in its pre-debug mode state, but any updates made in debug mode remain.

20.2

Memory Map/Register Definition

This section contains a memory map (see

) and describes the register structure for PIT0–PIT1.

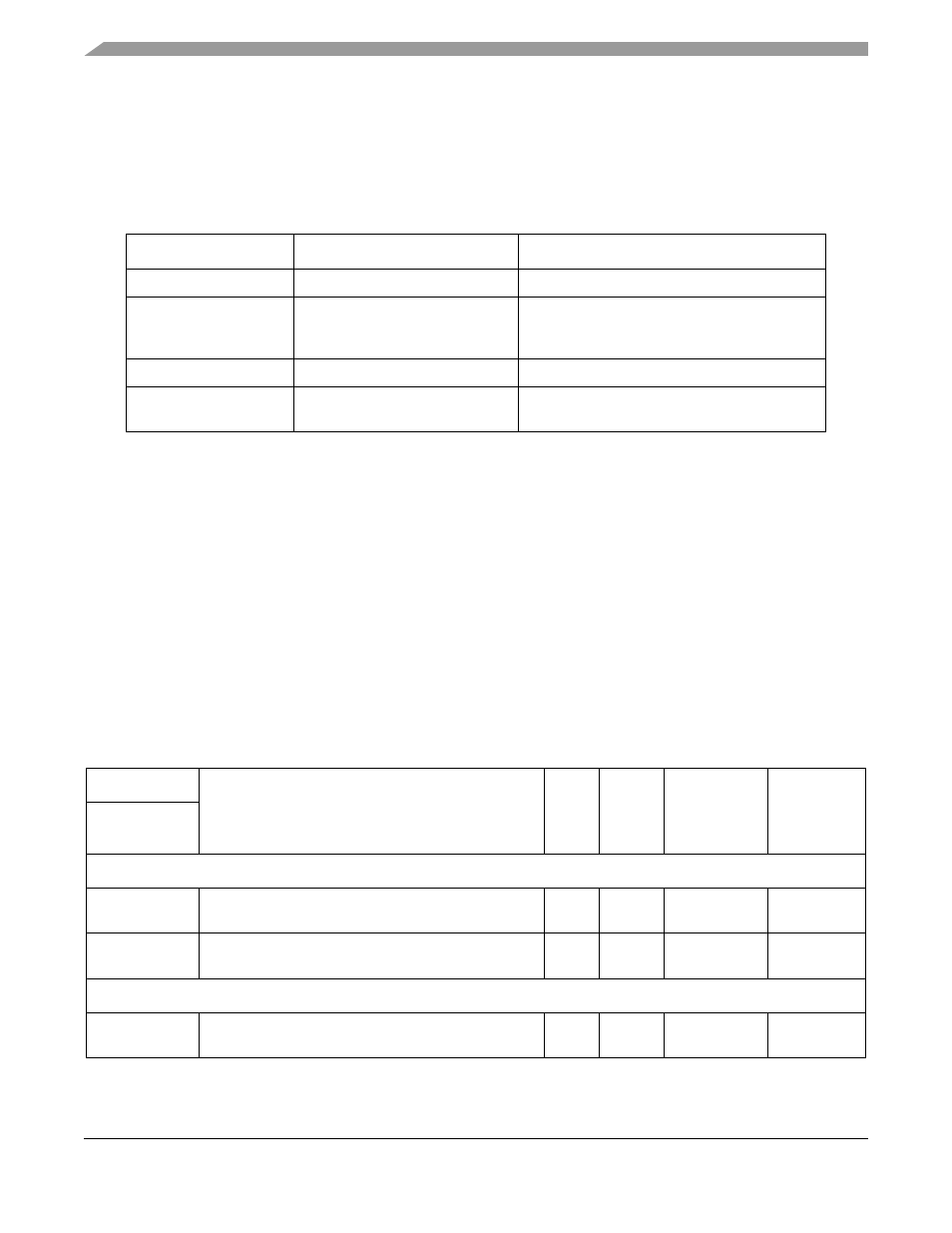

Table 20-1. PIT Module Operation in Low-power Modes

Low-power Mode

PIT Operation

Mode Exit

Wait

Normal

N/A

Doze

Normal if PCSRn[DOZE] cleared,

stopped otherwise

Any interrupt at or above level in LPICR, exit doze

mode if PCSRn[DOZE] is set. Otherwise

interrupt assertion has no effect.

Stop

Stopped

No

Debug

Normal if PCSRn[DBG] cleared,

stopped otherwise

No. Any interrupt is serviced upon normal exit

from debug mode

Table 20-2. Programmable Interrupt Timer Modules Memory Map

IPSBAR Offset

Register

Width

(bits)

Access

1

1

Accesses to reserved address locations have no effect and result in a cycle termination transfer error.

Reset Value

Section/Page

PIT 0

PIT 1

Supervisor Access Only Registers

2

0x15_0000

0x16_00000

PIT Control and Status Register (PCSRn)

16

R/W

0x0000

0x15_0002

0x16_0002

PIT Modulus Register (PMRn)

16

R/W

0xFFFF

User/Supervisor Access Registers

0x15_0004

0x16_0004

PIT Count Register (PCNTRn)

16

R

0xFFFF