3 peripheral power management set register (ppmrs) – Freescale Semiconductor ColdFire MCF52210 User Manual

Page 135

Power Management

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

Freescale Semiconductor

8-7

8.2.3

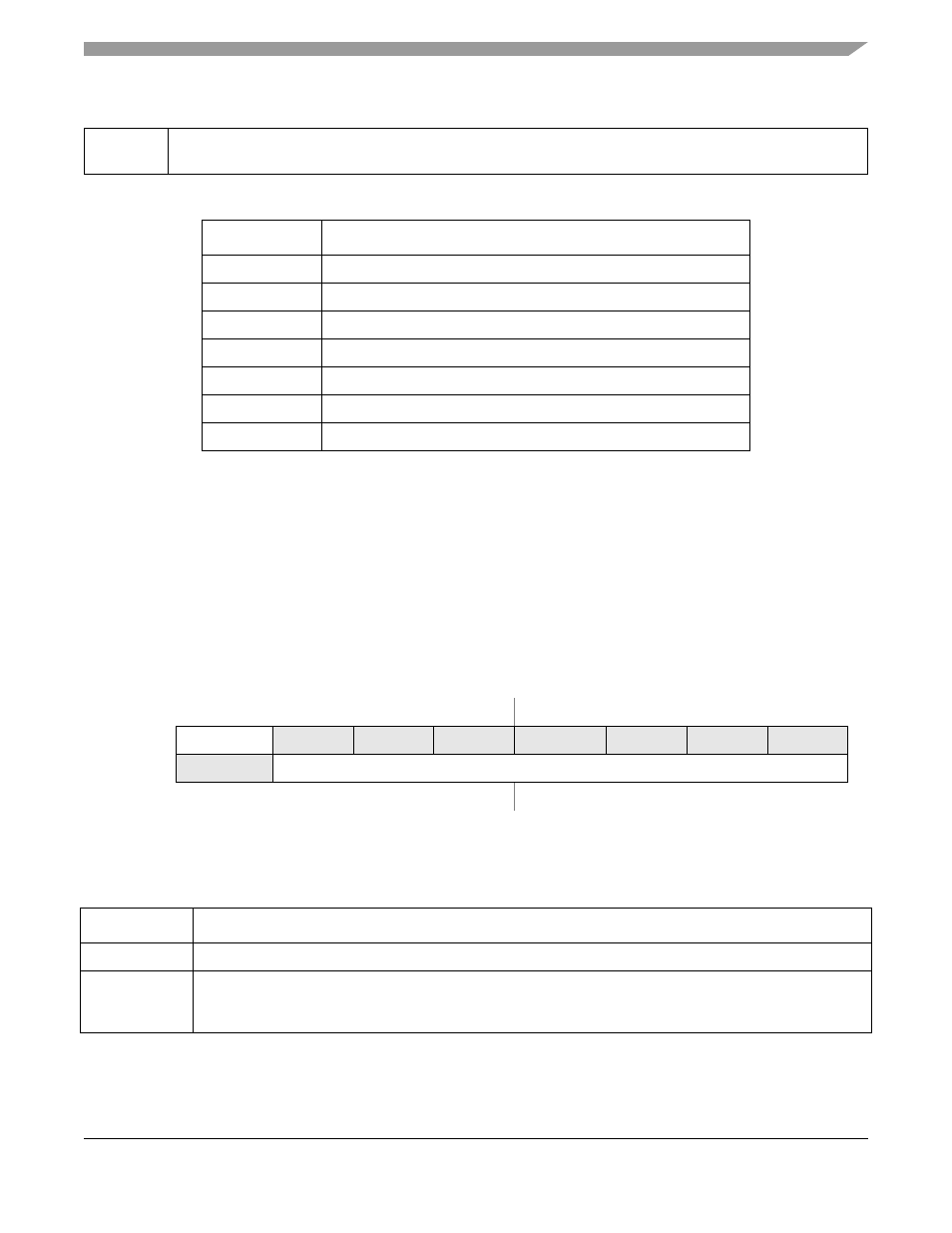

Peripheral Power Management Set Register (PPMRS)

The PPMRS register provides a simple memory-mapped mechanism to set a given bit in the PPMRx

registers to disable the clock for a given IPS module without the need to perform a read-modify-write on

the PPMR. The data value on a register write causes the corresponding bit in the PPMRx register to be set.

A data value of 64 to 127 provides a global set function, forcing the entire contents of the PPMRx to be

set, disabling all IPS module clocks. Reads of this register return all zeroes. See

for the PPMRS definition.

3–0

—

Reserved, should be cleared.

Table 8-5. XLPM_IPL Settings

XLPM_IPL[2:0]

Interrupts Level Needed to Exit Low-Power Mode

000

Any interrupt request exits low-power mode

001

Interrupt request levels 2–7 exit low-power mode

010

Interrupt request levels 3–7 exit low-power mode

011

Interrupt request levels 4–7 exit low-power mode

100

Interrupt request levels 5–7 exit low-power mode

101

Interrupt request levels 6–7 exit low-power mode

11x

Interrupt request level 7 exits low-power mode

IPSBAR

Offset: 0x0021 (PPMRS)

Access: write-only

7

6

5

4

3

2

1

0

R

0

W

PPMRS

Reset:

0

0

0

0

0

0

0

0

Figure 8-4. Peripheral Power Management Set Register (PPMRS)

Table 8-6. PPMRS Field Descriptions

Field

Description

7

Reserved, should be cleared.

6–0

PPMRS

Set Module Clock Disable

0–63 Set corresponding bit in PPMRx, disabling the module clock

64–127 Set all bits in PPMRx, disabling all the module clocks

Table 8-4. LPICR Field Description (continued)