Freescale Semiconductor ColdFire MCF52210 User Manual

Page 130

Power Management

MCF52211 ColdFire® Integrated Microcontroller Reference Manual, Rev. 2

8-2

Freescale Semiconductor

8.2.1

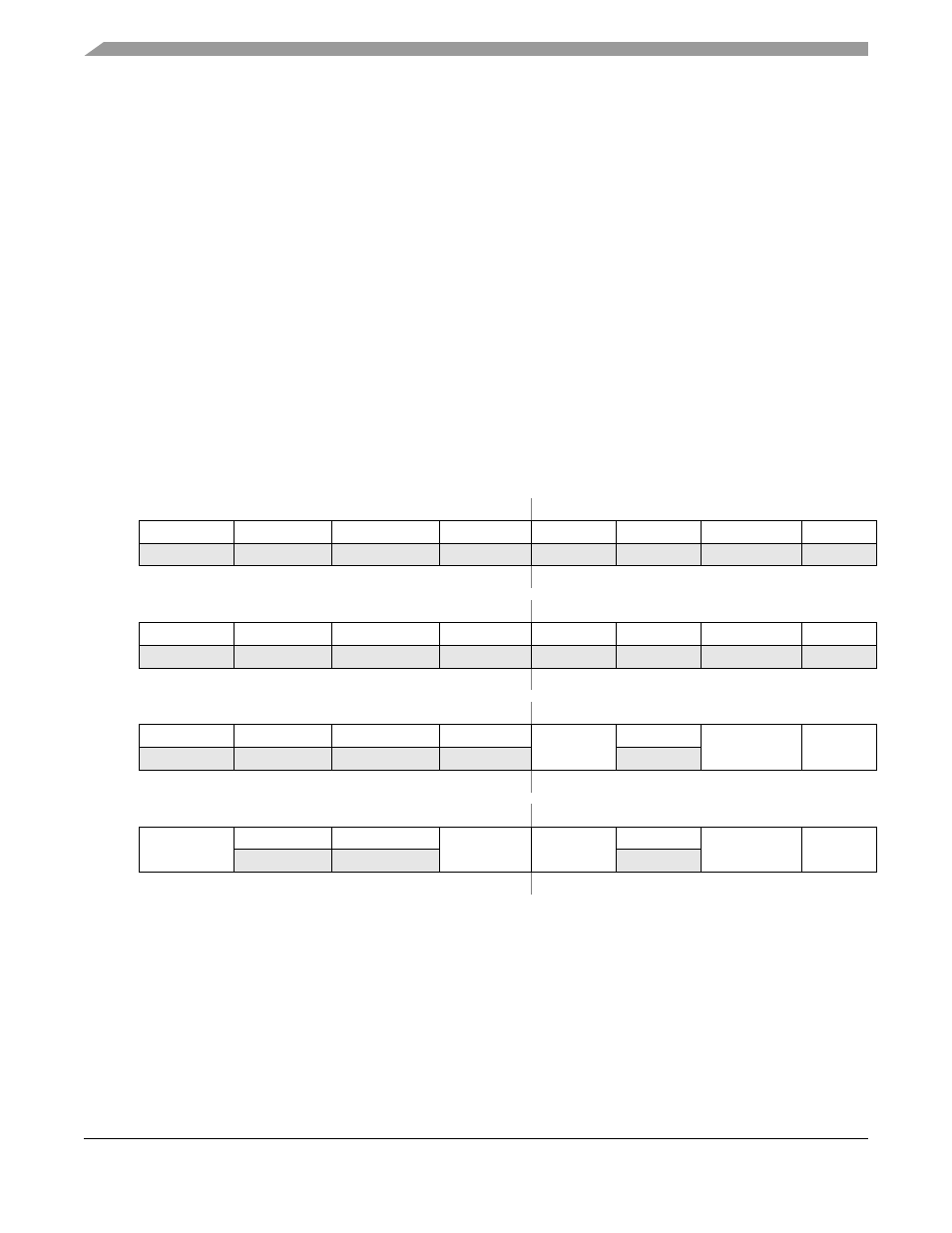

Peripheral Power Management Registers (PPMRH, PPMRL)

The PPMRH and PPMRL registers provide a bit map for controlling the generation of the module clocks

for each decoded address space associated with the IPS controller. The PPMRx provides a unique control

bit for each of these address spaces that defines whether the module clock for the given space is enabled

or disabled.

NOTE

It is software’s responsibility to appropriately disable module clocks using

the PPMRx only when a module is completely unused or quiescent.

Because the operation of the IPS controller and the system control module (SCM) are fundamental to the

operation of the system, the clocks for these three modules cannot be disabled.

The individual bits of the PPMRx can be modified using a read-modify-write to this register directly or

indirectly through writes to the PPMRS and PPMRC registers to set/clear individual bits.

See

and

for the PPMRH definition.

IPSBAR

Offset: 0x000C (PPMRH)

Access: read/write

31

30

29

28

27

26

25

24

R

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

23

22

21

20

19

18

17

16

R

0

0

0

0

0

0

0

0

W

Reset

0

0

0

0

0

0

0

0

15

14

13

12

11

10

9

8

R

0

0

0

0

CDCFM

0

CDPWM

CDGPT

W

Reset

0

0

0

0

0

0

0

0

7

6

5

4

3

2

1

0

R

CDADC

0

0

CDPIT1

CDPIT0

0

CDEPORT

CDPORTS

W

Reset

0

0

0

0

0

0

0

0

Figure 8-1. Peripheral Power Management Register High (PPMRH)