BECKHOFF ET1100 User Manual

Page 99

PDI description

Slave Controller

– ET1100 Hardware Description

III-85

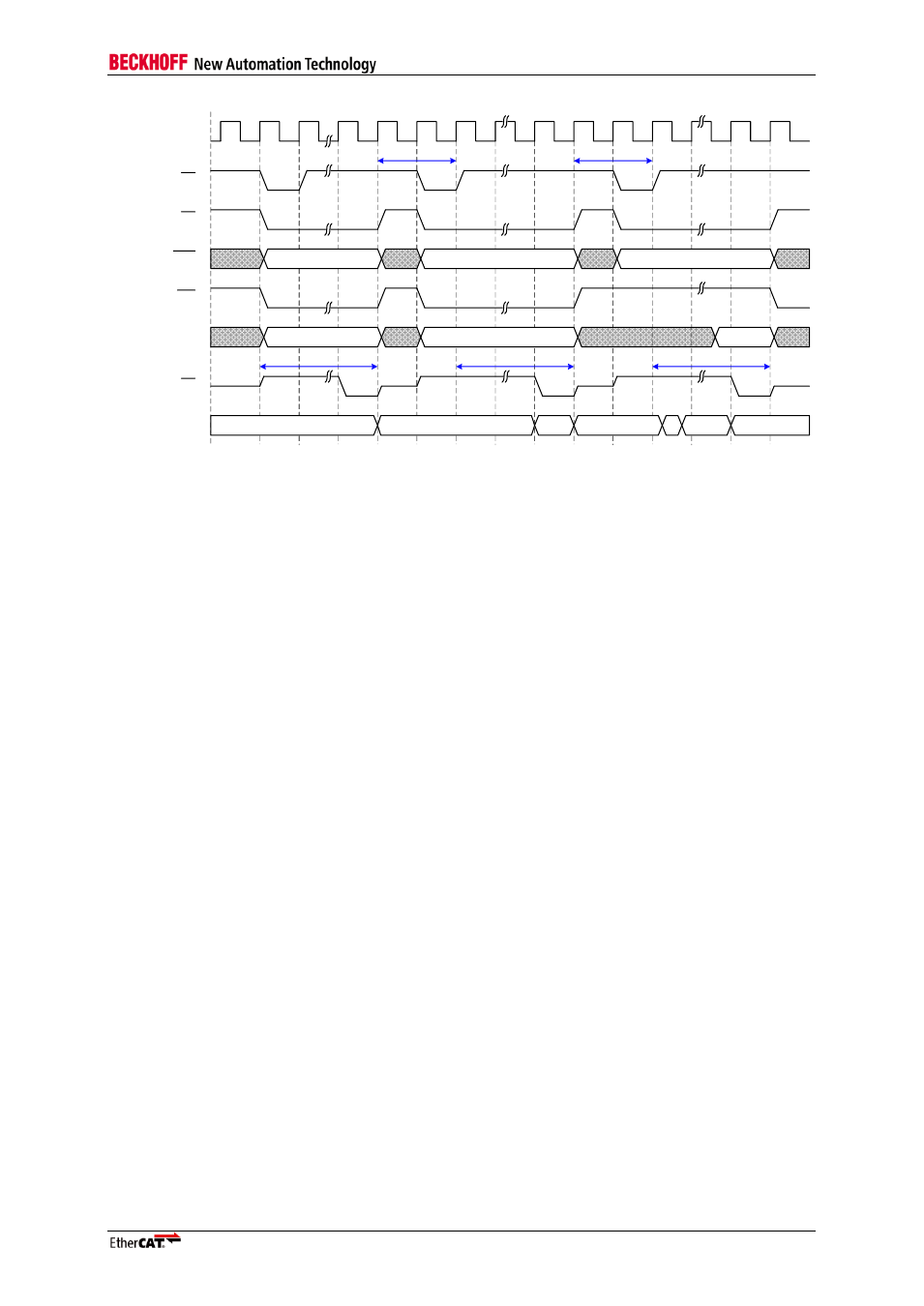

CPU_CLK_IN

TS

CS

ADR, BHE

DATA

TA

ADR1, BHE1

RD/WR

DATA1

t

Write

ADR2, BHE2

DATA2

t

Write

ADR3, BHE3

DATA3

t

Read

Internal state

Writing ADR1

Idle

Writing ADR2

Reading ADR3

Idle

Idle

Coll.

t

WR_delay

t

WR_to_RD

Figure 38: Sequence of two write accesses and a read access

Note: The first write access to ADR1 is performed after the first TA. After that, the ESC is internally busy writing to

ADR1. After CS is de-asserted, TA is not driven any more, nevertheless, the ESC is still writing to ADR1.

Hence, the second write access to ADR2 is delayed because the write access to ADR1 has to be completed first.

After the second TA, the ESC is busy writing to ADR2.

The third access in this example is a read access. The ESC is still busy writing to ADR2 while the read

access begins. In this case, the write access to ADR2 is finished first, and afterwards, the read access

to ADR3 is performed. The ESC signals TA after both write and read access have finished.