2 phy address configuration, Phy address configuration, Table 49: mii interface signals – BECKHOFF ET1100 User Manual

Page 58: Er 4.2

MII Interface

III-44

Slave Controller

– ET1100 Hardware Description

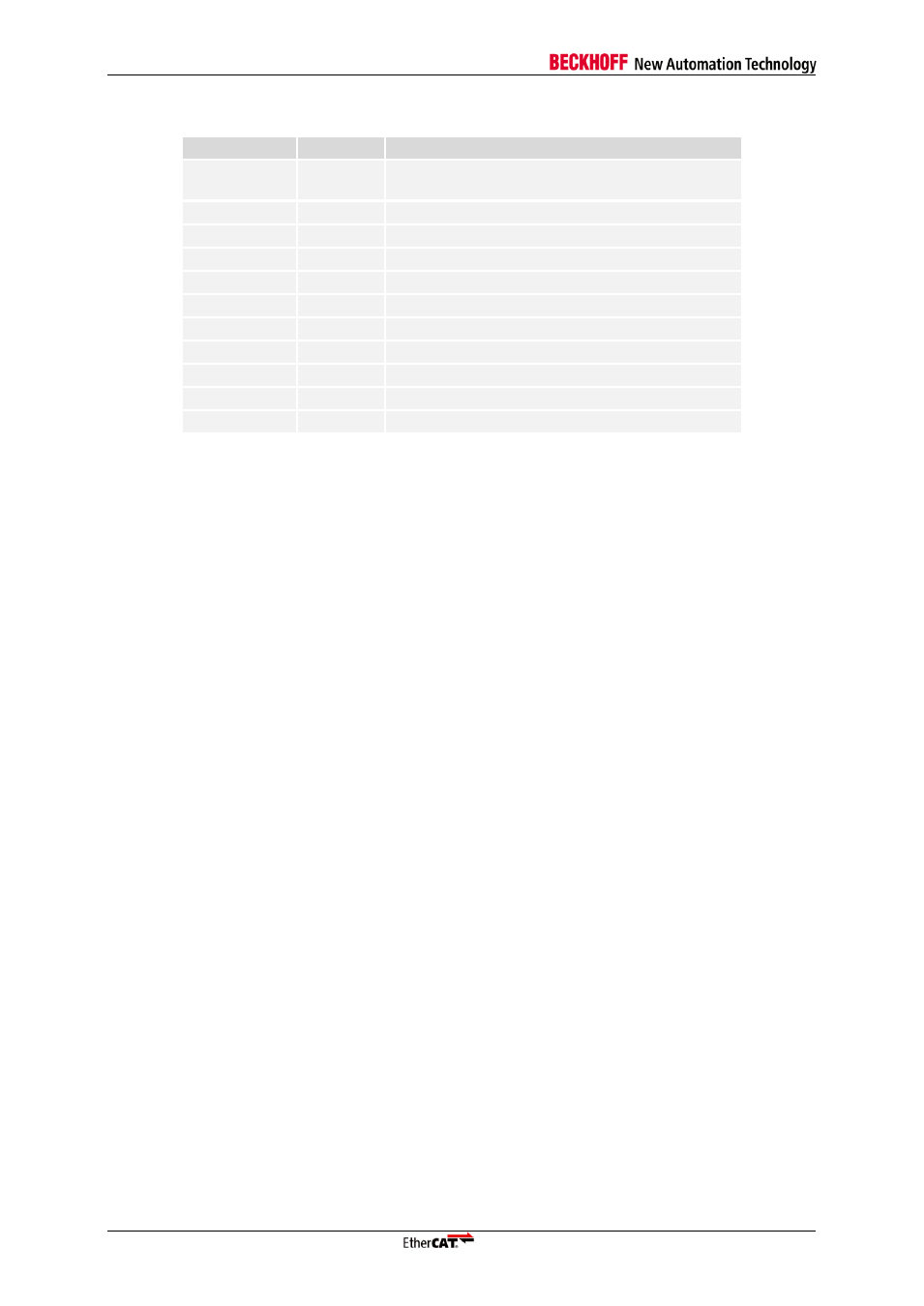

Table 49: MII Interface signals

Signal

Direction

Description

LINK_MII

IN

Input signal provided by the PHY if a 100 Mbit/s

(Full Duplex) link is established

RX_CLK

IN

Receive Clock

RX_DV

IN

Receive data valid

RX_D[3:0]

IN

Receive data (alias RXD)

RX_ERR

IN

Receive error (alias RX_ER)

TX_ENA

OUT

Transmit enable (alias TX_EN)

TX_D[3:0]

OUT

Transmit data (alias TXD)

MI_CLK

OUT

Management Interface clock (alias MCLK)

MI_DATA

BIDIR

Management Interface data (alias MDIO)

PHYAD_OFF

IN

Configuration: PHY address offset

LINKPOL

IN

Configuration: LINK_MII polarity

MI_DATA should have an external pull-up resistor (4.7 k

Ω recommended for ESCs). MI_CLK is driven

rail-to-rail, idle value is High.

4.2

PHY Address Configuration

The ET1100 addresses Ethernet PHYs using logical port number (or PHY address register value) plus

PHY address offset. Typically, the Ethernet PHY addresses should correspond with the logical port

number, so PHY addresses 0-3 are used.

A PHY address offset of 16 can be applied which moves the PHY addresses to 16-19 by inverting the

MSB of the PHY address internally.

If both alternatives cannot be used, the PHYs should be configured to use an actual PHY address

offset of 1, i.e., PHY addresses 1-4. The PHY address offset configuration of the ET1100 remains 0.

Refer to Section I for more details about PHY addressing.