7 digital control/status move, 8 phy address offset, 9 link polarity – BECKHOFF ET1100 User Manual

Page 33: Digital control/status move, Phy address offset, Link polarity, Table 21: digital control/status move, Table 22: phy address offset, Table 23: link polarity

Pin Description

Slave Controller

– ET1100 Hardware Description

III-19

3.2.7

Digital Control/Status Move

If more than 2 MII ports are used (PDI[39:32] are not available for PDI use), the Digital I/O PDI control

and status signals can be made available at the highest available PDI byte with

CTRL_STATUS_MOVE.

Digital Control/Status Move is explained in Table 21:

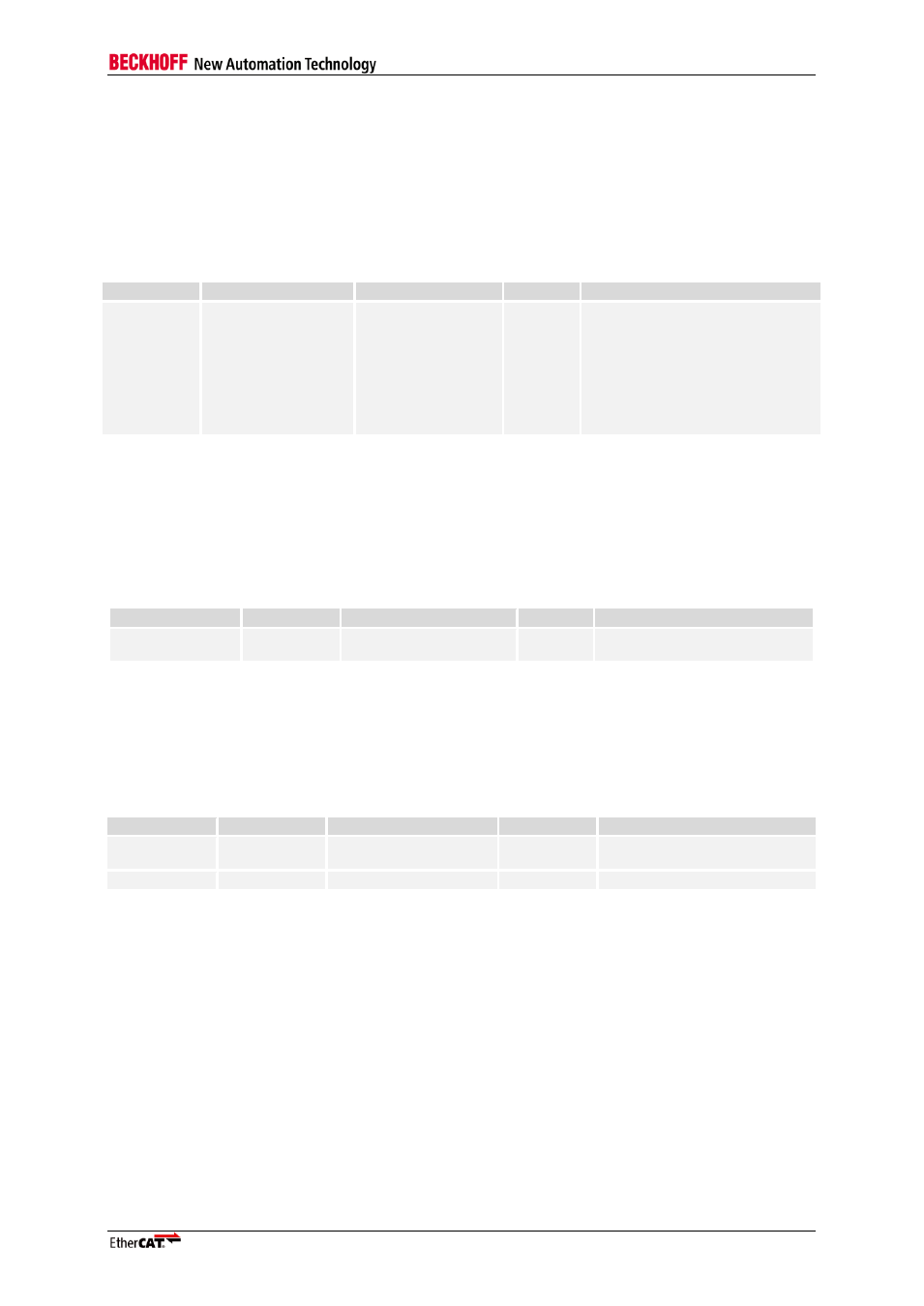

Table 21: Digital Control/Status Move

Description

Config signal

Pin name

Register

Values

Digital Control/

Status Move

CTRL_STATUS_MOVE

PDI[34]/TX_D(2)[0]/

CTRL_STATUS_MOVE

0x0E01[4]

0 = Digital I/O control/status signals are

not moved: they are available at

PDI[39:32] if less than 3 MII ports are

used, otherwise they are not available

1 = Digital I/O control/status signals

moved to last PDI byte if PDI[39:32] is

used for MII(2). Digital I/O control/status

signals are available in any

configuration.

3.2.8

PHY Address Offset

The ET1100 supports two PHY address offset configurations, either 0 or 16. Refer to chapter 4.2 for

details on PHY address configuration.

PHY Address Offset is explained in Table 22:

Table 22: PHY Address Offset

Description

Config signal

Pin name

Register

Values

PHY Address Offset

PHYAD_OFF

PERR(2)/TRANS(2)/

PHYAD_OFF

0x0E01[5]

0 = PHY address offset 0

1 = PHY address offset 16

3.2.9

Link Polarity

Ethernet PHYs signal a 100 Mbit/s Full (Duplex Link( to the ET1100 by asserting LINK_MII(x). The

polarity can be selected with LINKPOL.

Link Polarity is explained in Table 23:

Table 23: Link Polarity

Description

Config signal

Pin name

Register

Values

Link Polarity

LINKPOL

MI_CLK/LINKPOL

0x0E01[6]

0 = LINK_MII(x) is active low

1 = LINK_MII(x) is active high

Reserved

RESERVED

PDI[28]/PERR(3)/TRANS(3)

0x0E01[7]

reserved