6 interrupt request register (al event register), 7 write access, 8 read access – BECKHOFF ET1100 User Manual

Page 71: 1 read wait state, 2 read termination, Interrupt request register (al event register), Write access, Read access, Table 61: interrupt request register transmission

PDI description

Slave Controller

– ET1100 Hardware Description

III-57

Table 60: Address modes for Read access with Wait state byte

Byte

2 Byte address mode

3 Byte address mode

0

A[12:5]

address bits [12:5]

A[12:5]

address bits [12:5]

1

A[4:0]

address bits [4:0]

CMD0[2:0] read command: 011b

A[4:0]

address bits [4:0]

CMD0[2:0] 3 byte addressing: 110b

2

0xFF

wait state byte

A[15:13]

address bits [15:13]

CMD1[2:0] read command: 011b

res[1:0]

two reserved bits, set to 00b

3

D0[7:0]

data byte 0

0xFF

wait state byte

4

D1[7:0]

data byte 1

D0[7:0]

data byte 0

5 ff.

D2[7:0]

data byte 2

D1[7:0]

data byte 1

6.3.6

Interrupt request register (AL Event register)

During the address phase, the SPI slave transmits the PDI interrupt request registers 0x0220-0x0221

(2 byte address mode), and additionally register 0x0222 for 3 byte addressing on SPI_DO (MISO):

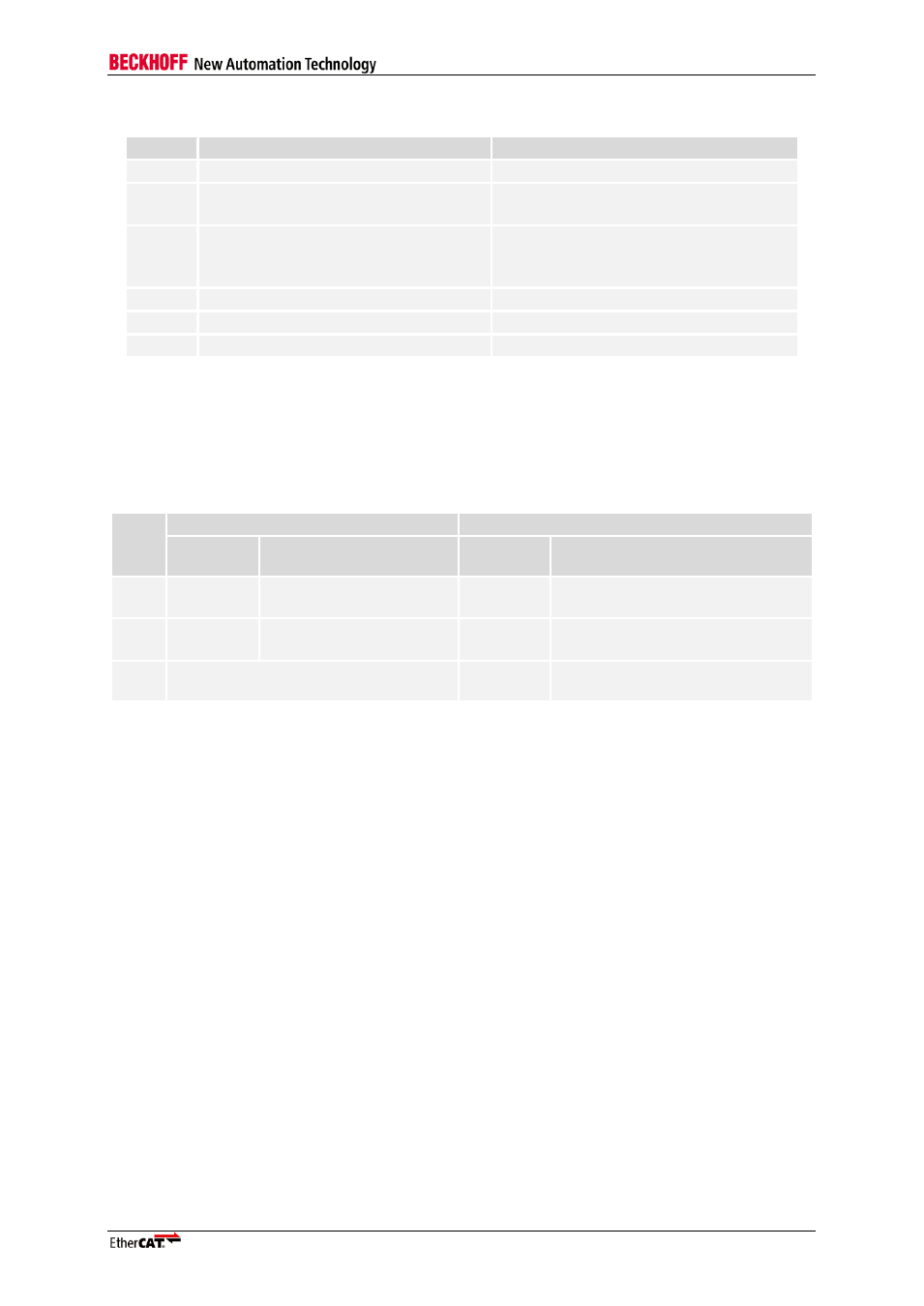

Table 61: Interrupt request register transmission

Byte

2 Byte address mode

3 Byte address mode

SPI_DI

(MOSI)

SPI_DO

(MISO)

SPI_DI

(MOSI)

SPI_DO

(MISO)

0

A[12:5]

I0[7:0]

interrupt request

register 0x0220

A[12:5]

I0[7:0]

interrupt request register

0x0220

1

A[4:0]

CMD0[2:0]

I1[7:0]

interrupt request

register 0x0221

A[4:0]

CMD0[2:0]

I1[7:0]

interrupt request register

0x0221

2

(Data phase)

A[15:13]

CMD1[2:0]

I2[7:0]

interrupt request register

0x0222

6.3.7

Write access

In the data phase of a write access, the SPI master sends the write data bytes to the SPI slave

(SPI_DI/MOSI). The write access is terminated by taking back SPI_SEL after the last byte. The

SPI_DO signal (MISO) is undetermined during the data phase of write accesses.

6.3.8

Read access

In the data phase of a read access, the SPI slave sends the read data bytes to the SPI master

(SPI_DO/MISO).

6.3.8.1

Read Wait State

Between the last address phase byte and the first data byte of a read access, the SPI master has to

wait for the SPI slave to fetch the read data internally. Subsequent read data bytes are prefetched

automatically, so no further wait states are necessary.

The SPI master can choose between these possibilities:

The SPI master may either wait for the specified worst case internal read time t

read

after the last

address/command byte and before the first clock cycle of the data phase.

The SPI master inserts one Wait State byte after the last address/command byte. The Wait State

byte must have a value of 0xFF transferred on SPI_DI.

6.3.8.2

Read Termination

The SPI_DI signal (MOSI) is used for termination of the read access by the SPI master. For the last

data byte, the SPI master has to set SPI_DI to high (Read Termination byte = 0xFF), so the slave will