7 distributed clocks sync/latch signals, 1 signals, 2 timing specifications – BECKHOFF ET1100 User Manual

Page 100: Distributed clocks sync/latch signals, Signals, Timing specifications, Table 76: distributed clocks signals, Figure 39: distributed clocks signals, Figure 40: latchsignal timing, Figure 41: syncsignal timing

Distributed Clocks SYNC/LATCH Signals

III-86

Slave Controller

– ET1100 Hardware Description

7

Distributed Clocks SYNC/LATCH Signals

For details about the Distributed Clocks refer to Section I.

7.1

Signals

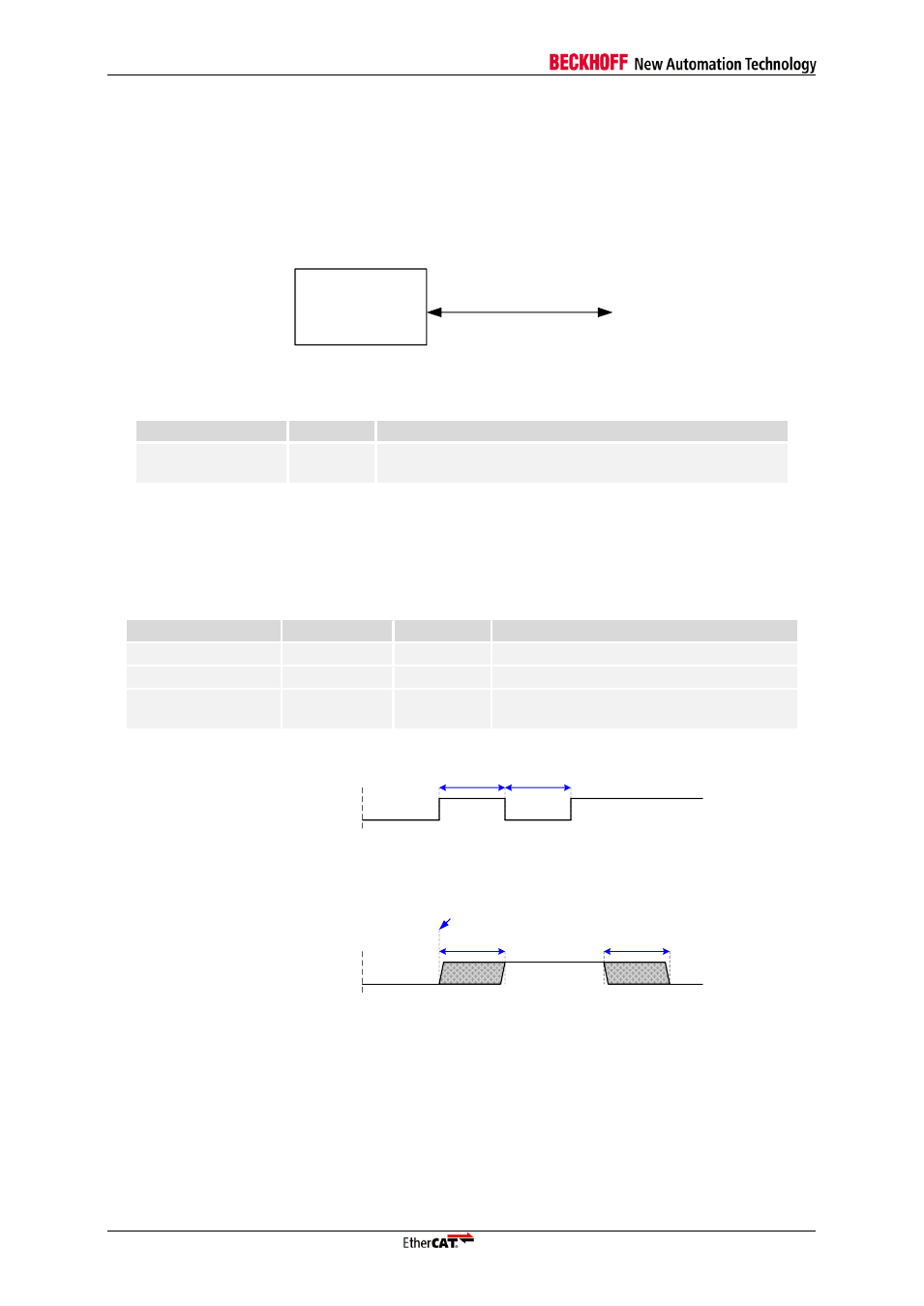

The Distributed Clocks unit of the ET1100 has the following external signals:

EtherCAT

device

SYNC/LATCH[1:0]

Figure 39: Distributed Clocks signals

Table 76: Distributed Clocks signals

Signal

Direction

Description

SYNC/LATCH[1:0]

OUT/IN

SyncSignal (OUT) or LatchSignal (IN), direction bitwise

configurable via register 0x0151 / EEPROM.

NOTE: SYNC/LATCH signals are not driven (high impedance) until the SII EEPROM is loaded.

7.2

Timing specifications

Table 77: DC SYNC/LATCH timing characteristics ET1100

Parameter

Min

Max

Comment

t

DC_LATCH

15 ns

Time between Latch0/1 events

t

DC_SYNC_Jitter

15 ns

SYNC0/1 output jitter

t

DC_SYNC_Pulse_IRQ

40 ns

Pulse length for SYNC0/1 if used as PDI

interrupt in continuous mode

LATCH0/1

t

DC_LATCH

t

DC_LATCH

Figure 40: LatchSignal timing

SYNC0/1

t

DC_SYNC_Jitter

Output event time

t

DC_SYNC_Jitter

Figure 41: SyncSignal timing