10 timing specification, Timing specification – BECKHOFF ET1100 User Manual

Page 96

PDI description

III-82

Slave Controller

– ET1100 Hardware Description

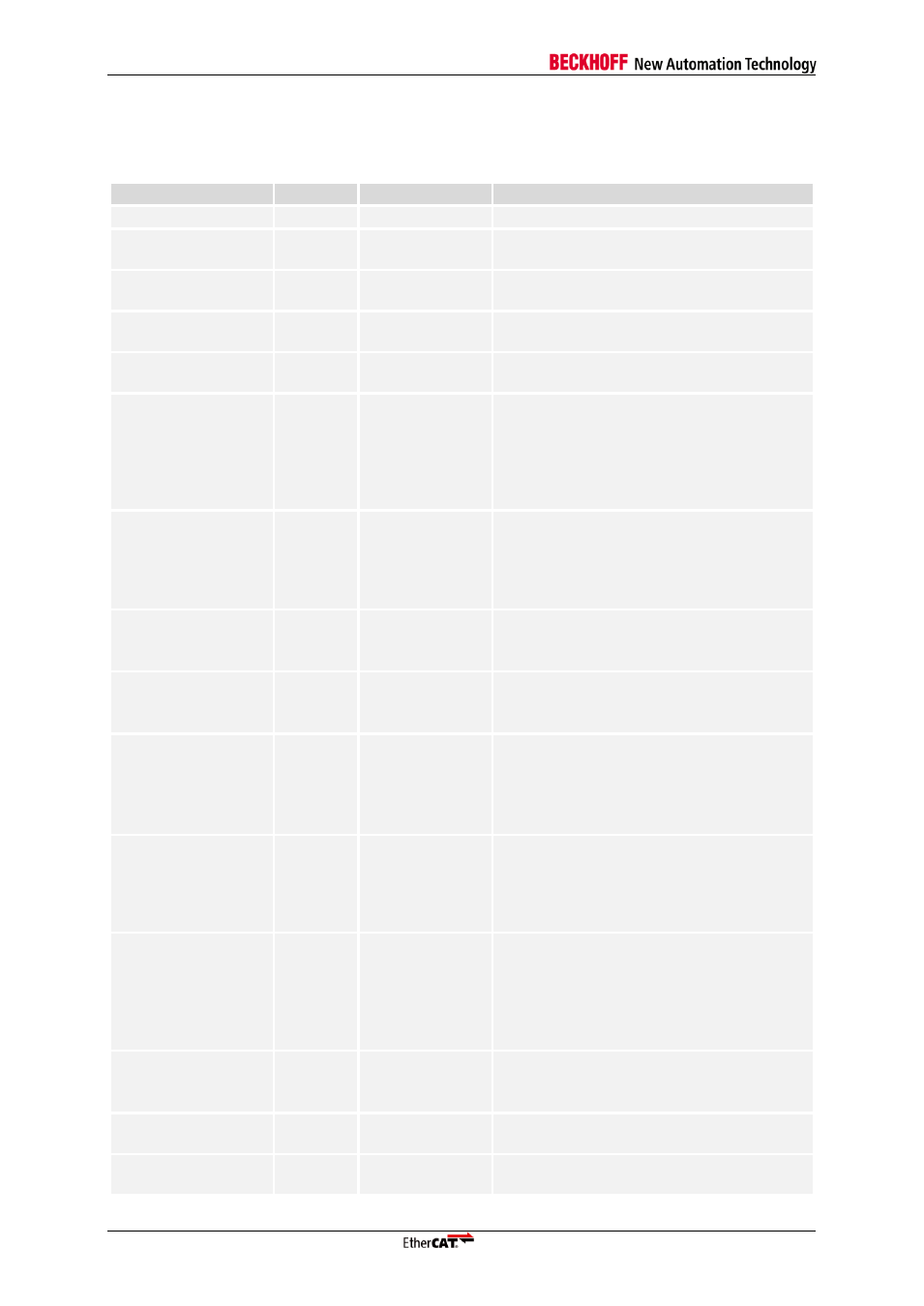

6.5.10 Timing Specification

Table 75: µController timing characteristics ET1100

Parameter

Min

Max

Comment

t

CLK

25 ns

CPU_CLK_IN period (f

CLK

≤ 40 MHz)

t

IN_setup

10 ns

Input signals valid before CPU_CLK_IN

edge (TS, CS, ADR, BHE, R/nW, DATA)

t

IN_hold

3 ns

Input signals valid after CPU_CLK_IN edge

(TS, CS, ADR, BHE, R/nW, DATA)

t

CLK_to_OUT_valid

15 ns

Output signals valid after CPU_CLK_IN

edge (TA, IRQ, DATA)

t

CLK_to_OUT_invald

0 ns

Output signals invalid after CPU_CLK_IN

edge (TA, IRQ, DATA)

t

read

a) t

read_int

+ t

prec_write

+t

Coll

b) t

read_int

+t

read_sync

External read time (TS to TA)

a) with preceeding write access and

t

WR_to_RD +

t

read_sync <

t

prec_write

+ t

Coll

b) without preceeding write access or

t

WR_to_RD +

t

read_sync >

t

prec_write

+ t

Coll

t

read_sync

2.5*t

CLK

a) +0.5*t

CLK

b) +0.5*t

CLK

c) +t

CLK

Extra read synchronization delay

a) extra delay if 0x0152.11=1

b) extra delay if 0x0152.10=1

b) extra delay if CS asserted one

CPU_CLK_IN cycle after TS

t

read_int

a) 235 ns

b) 315 ns

Internal read time

a) 8 bit access

b) 16 bit access

t

prec_write

a) 180 ns

b) 260 ns

Time for preceding write access

a) 8 bit access

b) 16 bit access

t

Coll

a) 20 ns

b) 0 ns

Extra read delay

a) RD access directly follows WR access

with the same address (8 bit accesses or 8

bit WR and 16 bit RD)

b) different addresses or 16 bit accesses

t

write

a) t

write_int

b) t

write_sync

External write time (TS to TA)

a) with preceeding write access and

t

WR_delay

+t

write_sync

< t

write_int

b) without preceeding write access or

t

WR_delay

+t

write_sync

≥ t

write_int

t

write_sync

2.5*t

CLK

a) +t

CLK

b) +0.5*t

CLK

c) +0.5*t

CLK

d) +t

CLK

Extra write synchronization delay

a) extra delay if 0x0152.8=0

b) extra delay if 0x0152.10=1

c) extra delay if 0x0152.11=1

d) extra delay if CS asserted one

CPU_CLK_IN cycle after TS

t

write_int

a) 200 ns

b) 280 ns

Internal write time

a) 8 bit access

b) 16 bit access

t

write+read

t

write

+t

read

Internal write/read time for a read access

following a write access

t

EEPROM_LOADED_to_access

0 ns

Time between EEPROM_LOADED and first

access