3 µcontroller access, Μcontroller access, Table 71: corresponding bytes and bits – BECKHOFF ET1100 User Manual

Page 89: Table 72: byte ordering

PDI description

Slave Controller

– ET1100 Hardware Description

III-75

6.5.3

µController access

The 8 bit µController interface reads or writes 8 bit per access, the 16 bit µController interface

supports both 8 bit and 16 bit read/write accesses. The least significant address bit A[0] together with

Byte High Enable (BHE) are used to distinguish between 8 bit low byte access, 8 bit high byte access

and 16 bit access.

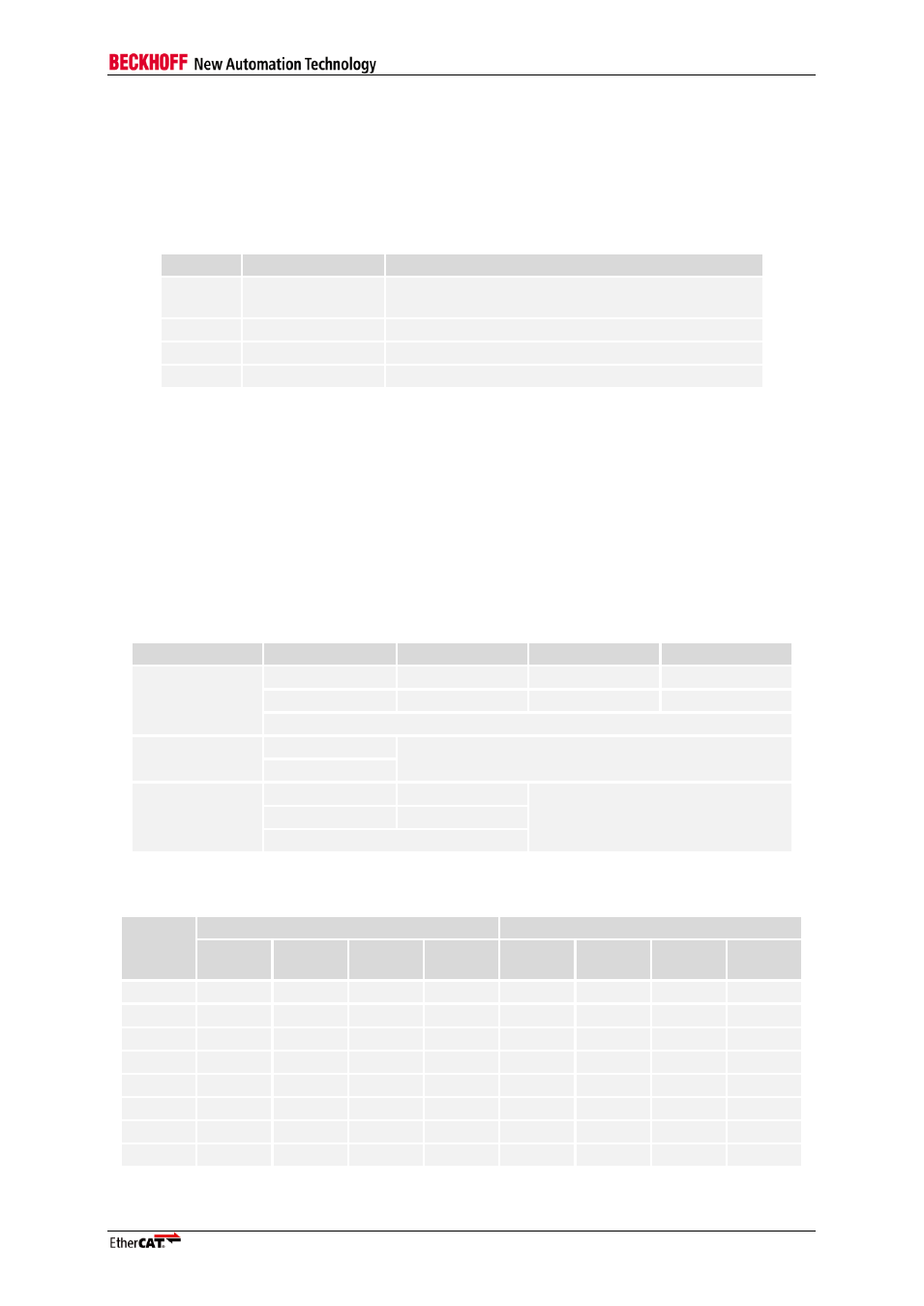

Table 70: 8 bit high/low byte and 16 bit access distinction

ADR[0]

BHE (act. low)

Access

0

0

16 bit access to ADR[15:0] and ADR[15:0]+1 (low

and high byte)

0

1

8 bit access to ADR[15:0] (low byte, even address)

1

0

8 bit access to ADR[15:0] (high byte, odd address)

1

1

invalid access

If Byte High Enable (BHE) is used, the Byte access mode configuration bit has to be set to zero (BHE

or Byte Select mode).

EtherCAT devices use Little Endian byte ordering, even with the synchronous µController interface.

The conversion between Little Endian and Big Endian, depending on the register size of 8, 16, 32, or

64 bit, has to be done in software.

NOTE: A µController with 32 Bit interface is used as an example connected to the synchronous µController

interface. It is also possible to use 8 or 16 Bit µControllers.

NOTE: Please compare the bit ordering ([0:31] instead of [31:0]) of your µController with that used in this

document, because it might be different. The MSB/LSB notation used below will help you.

Table 71: Corresponding Bytes and Bits

Address

0

1

2

3

µController

[31:24]

[23:16]

[15:8]

[7:0]

[MSBit:LSBit]

[MSBit:LSBit]

[MSBit:LSBit]

[MSBit:LSBit]

MSByte : LSByte

ESC 8 Bit

access

[7:0]

[MSBit:LSBit]

ESC 16 Bit

access

[7:0]

[15:8]

[MSBit:LSBit]

[MSBit:LSBit]

LSByte : MSByte

Table 72: Byte ordering

Addr.

ESC (Little Endian)

sync. µController (Big Endian)

8 bit

reg.

16 bit

reg.

32 bit

reg.

64 bit

reg.

8 bit

reg.

16 bit

reg.

32 bit

reg.

64 bit

reg.

0

Byte 0

LSB

LSB

LSB

Byte 0

MSB

MSB

MSB

1

Byte 1

MSB

|

|

Byte 1

LSB

|

|

2

Byte 2

LSB

|

|

Byte 2

MSB

|

|

3

Byte 3

MSB

MSB

|

Byte 3

LSB

LSB

|

4

Byte 4

LSB

LSB

|

Byte 4

MSB

MSB

|

5

Byte 5

MSB

|

|

Byte 5

LSB

|

|

6

Byte 6

LSB

|

|

Byte 6

MSB

|

|

7

Byte 7

MSB

MSB

MSB

Byte 7

LSB

LSB

LSB