Document history – BECKHOFF ET1100 User Manual

Page 3

DOCUMENT HISTORY

Slave Controller

– ET1100 Hardware Description

III-III

DOCUMENT HISTORY

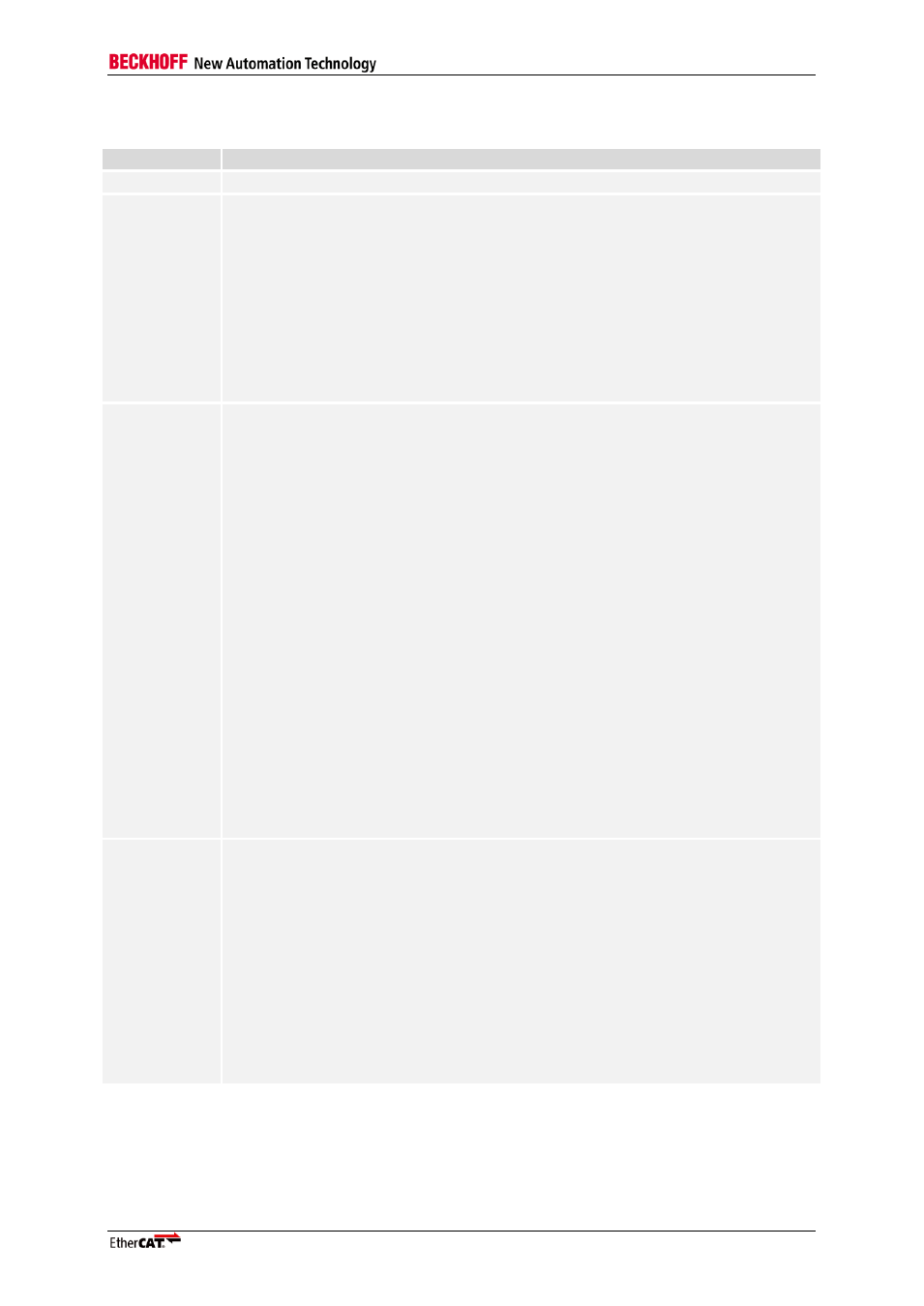

Version

Comment

0.6

Editorial Changes

0.7

Synchronous µController Interface LSB/MSB clarification table added

EEPROM_LOADED pull-down recommendation added

Chip label updated

VCC

I/O

/GND

I/O

pins adjacent to LDO indicated

Frame processing order example corrected

I

2

C EEPROM interface description added

MII management interface description added

Corrected Process RAM size in Register Overview

P_CONF does not correspond with physical ports. See new port configuration

tables for details.

Revision/Build information added

0.8

CLK25OUT1/2 availability completed

Recommendations for unused input pins added (should not be left open)

EEPROM_SIZE description corrected from Kbyte to Kbit, possible EEPROM

sizes range from 16 Kbit to 4 Mbit

RoHS compliance added

Autonegotiation is mandatory for ESCs

Description of power supply options added

Electrical characteristics added/revised

SPI_IRQ delay added, support for SPI masters with 2 or 4 bytes added

TX Shift timing diagram and description added

Internal 27 k

Ω PU/PD resistors at EBUS-RX pins added

LED polarity depending on configuration pin setting described

Recommendation for voltage stabilization capacitors added

Description of Digital I/O behavior on watchdog expiration enhanced

8 bit asynchronous µController PDI connection added

EBUS ports are open failsafe

Reset example schematic added

Ethernet PHY requirements and PHY connection schematic added

MI_DATA pull-up requirement added

µController PDI: DATA bus signal direction corrected

Pin/Signal description overview added

PERR(x) LEDs are only for testing/debugging

Editorial changes

1.0

RUN, LINKACT/x) and PERR(x) LED activity level corrected: active high if pulled

down, active low if pulled up

DC Characteristics enhanced: added V

Reset Core

, V

ID

, V

IC

Synchronous µController interface: timing characteristics enhanced

Note on RBIAS if no EBUS ports/only MII ports are used

DC SYNC/LATCH signal description and timing characteristics added

MII Interface chapter and MII timing characteristics added

EBUS Interface chapter added

Frame processing order, PHY requirements, EEPROM Interface description and

MII Management Interface description moved to Section I

TX Shift description moved to MII Interface chapter

Ambient temperature range instead of junction temperature range

Editorial changes