2 configuration pins, 1 port mode, 2 port configuration – BECKHOFF ET1100 User Manual

Page 28: Configuration pins, Port mode, Port configuration, Table 11: port mode, Table 12: port configuration

Pin Description

III-14

Slave Controller

– ET1100 Hardware Description

3.2

Configuration Pins

The configuration pins are used to configure the ET1100 at power-on with pull-up or pull-down

resistors. At power-on the ET1100 uses these pins as inputs to latch the configuration

2

. After power-

on, the pins have their operation functionality which has been assigned to them, and therefore pin

direction changes if necessary. The power-on phase finishes before the nRESET pin is released. In

subsequent reset phases without power-on condition, the configuration pins still have their operation

functionality, i.e., the ET1100 configuration is not latched again and output drivers remain active.

The configuration value 0 is realized by a pull-down resistor, a pull-up resistor is used for a 1. Since

some configuration pins are also used as LED outputs, the polarity of the LED output depends on the

configuration value.

3.2.1

Port Mode

Port Mode configures the number of physical ports and the corresponding logical ports. It is shown in

Table 11.

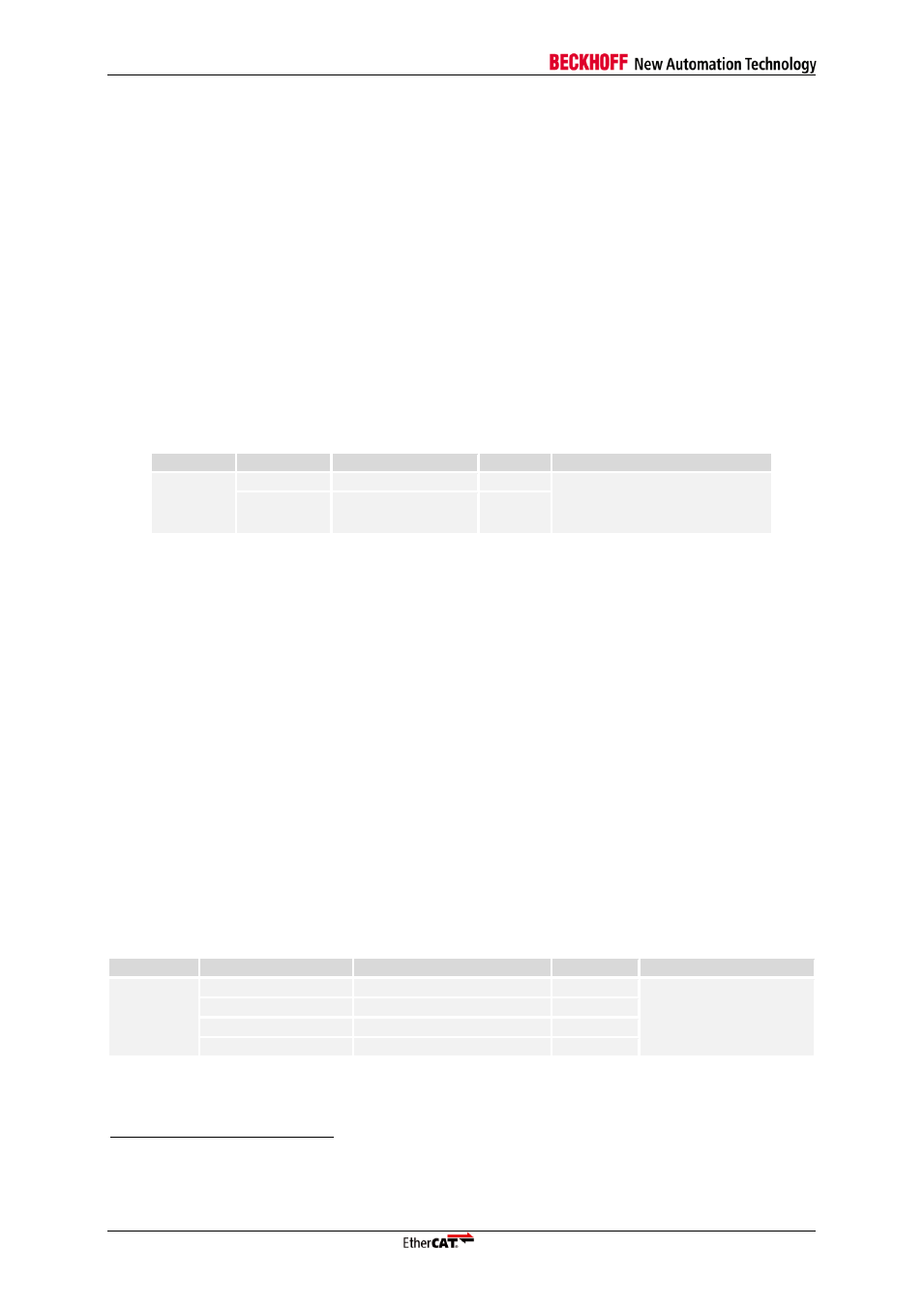

Table 11: Port Mode

Description

Config signal

Pin name

Register

P_MODE[1:0] Values

Port Mode

P_MODE[0]

TX_D(1)[2]/P_MODE[0]

0x0E00[0]

00 = 2 ports (log. ports 0 and 1)

01 = 3 ports (log. ports 0,1, and 2)

10 = 3 ports (log. ports 0,1, and 3)

11 = 4 ports (log. ports 0, 1, 2, and 3)

P_MODE[1]

TX_D(1)[3]/P_MODE[1]

0x0E00[1]

NOTE: The term physical port in this document is only used for grouping ET1100 interface pins. The register set

as well as any master/slave software is always based on logical ports. The distinction between physical and

logical ports is made in order to increase the number of available PDI pins. Each logical port is associated with

exactly one physical port, and it can be configured to be either EBUS or MII.

MII ports are always assigned to the lower physical ports, then EBUS ports are assigned. If any MII

ports are configured, the lowest logical MII port is always connected to physical port 0, the next higher

logical MII port is connected to physical port 1, and so on. Afterwards, the lowest logical EBUS port

– if

configured

– is connected to the next physical port following the physical MII ports, i.e. port [number of

MII ports]. Without MII ports, the EBUS ports are connected beginning with physical port 0.

If only EBUS or only MII ports are used, the physical port number is the same as the logical port

number for P_MODE[1:0]=00, 01 or 11. Refer to the next chapter for more details.

3.2.2

Port Configuration

P_CONF[3:0] determines the physical layer configuration (MII or EBUS). P_CONF[0] determines the

physical layer of logical port 0, P_CONF[1] determines logical port 1, P_CONF[2] determines the

physical layer of the next available logical port (either 3 for P_MODE[1:0]=10, else 2), and P_CONF[3]

determines logical port 3. If a physical port is not used, the corresponding P_CONF configuration

signal is not used.

Table 12: Port Configuration

Description

Configuration signal

Pin name

Register

Values

Port

Configuration

P_CONF[0]

LINKACT(0)/P_CONF[0]

0x0E00[2]

0 = EBUS

1 = MII

P_CONF[1]

LINKACT(1)/P_CONF(1)

0x0E00[3]

P_CONF[2]

LINKACT(2)/P_CONF[2]

0x0E00[4]

P_CONF[3]

PDI[30]/LINKACT(3)/P_CONF(3)

0x0E00[5]

2

Take care of proper configuration: External devices attached to dual-purpose configuration pins might interfere

sampling the intended configuration if they are e.g. not properly powered at the sample time (external device

keeps configuration pin low although a pull-up resistor is attached). In such cases the ET1100 power-on value

sampling time can be delayed by delaying power activation.