13 interrupt structure, Table 4-8, Interrupt mapping – Artesyn ATCA-F125 Installation and Use Guide (April 2014) User Manual

Page 97: Functional description

Functional Description

ATCA-F125 (6873M Artwork) Installation and Use (6806800J94J)

97

4.13 Interrupt Structure

All external interrupts belonging to the service processor interrupt structure are routed to the

P2020 QorIQ Integrated Processor. The PIC inside the P2020 QorIQ Integrated Processor is

compliant with the OpenPIC architecture.

The interrupt controller provides interrupt management, and is responsible for receiving

hardware-generated interrupts from different sources (both internal and external), prioritizing

them, and delivering them to the CPU for servicing. The PIC is set to the mixed mode on ATCA-

F125 so that both internal and external interrupts are delivered using normal priority and

delivery mechanisms.

Some interrupt sources are collected by the onboard FPGA. This FPGA includes an interrupt

source register, which reflects the actual interrupt status. The interrupt inputs of the FPGA are

mapped to the IRQ[11:0] signals, which are connected to the P2020 QorIQ Integrated

Processor.

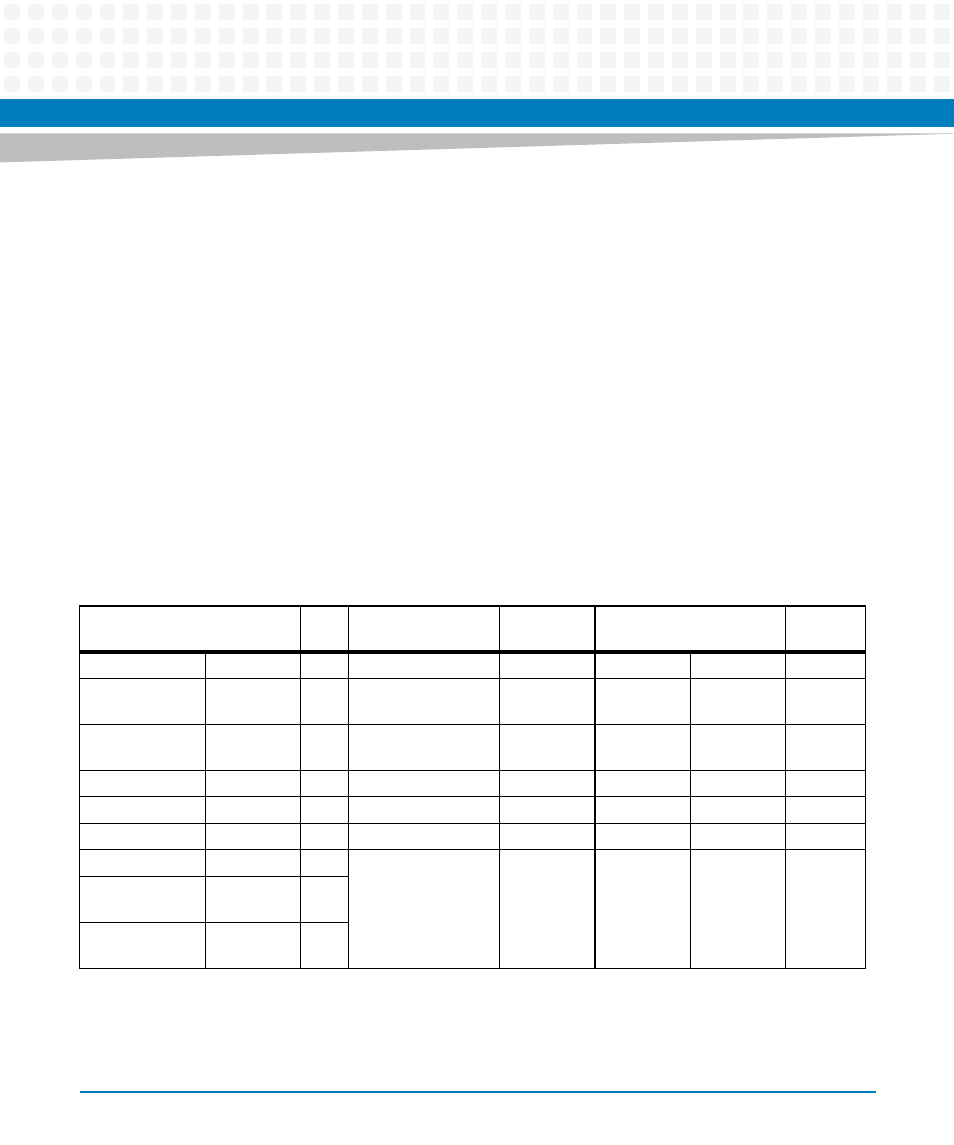

Table 4-8 Interrupt Mapping

Interrupt Source

Port Signal

Source

Type

P2020

IRQ

BCM56334

INTA

P2020 PCIE 1 INTA

Internal

0

BITS Framer 1

DS26503

INT_L

BITS1_INT_L

Direct

Active Low

OD

1

BITS Framer 2

DS26503

INT_L

BITS2_INT_L

Direct

Active Low

OD

2

DIMMs

EVENT_L

DIMM_EVENT_L

Direct

Active Low

OD

3

88SE6121 SATA

INTA

P2020 PCI2 INTA

Internal

4

RTM FPGA

INT_L

RTM_INT_L

Direct

Active Low

LVTTL

5

FPGA UART

UART_INT

SP_IRQ_6

FPGA

(ORed)

Active Low

LVTTL

6

IPMC LPC

SERIRQ_IN

TOUT

Watchdog

Timer

1st stage

WDT