1 service processor core reset domain, 1 service processor, Table 4-7 – Artesyn ATCA-F125 Installation and Use Guide (April 2014) User Manual

Page 94: Reset signals, Functional description

Functional Description

ATCA-F125 (6873M Artwork) Installation and Use (6806800J94J)

94

A software controlled reset register within the FPGA will provide software controlled resets to

the FIX, BIX and PHY functions. The FPGA will also implement a last reset register to capture the

source of the last reset generated on the board.

4.12.1 Service Processor Core Reset Domain

The service processor core includes the P2020 QorIQ Integrated Processor, its memory and the

onboard resources attached to the local bus.

4.12.1.1 Service Processor

The hard reset signal HRST_L causes the P2020 QorIQ Integrated Processor to abort all current

internal and external transactions and set all registers to their default values. HRST_L may be

asserted at any time completely asynchronously. HRST_L needs to be asserted during power-

on reset. During HRST_L assertion, the configuration input signals are sampled into registers

inside the P2020 QorIQ Integrated Processor.

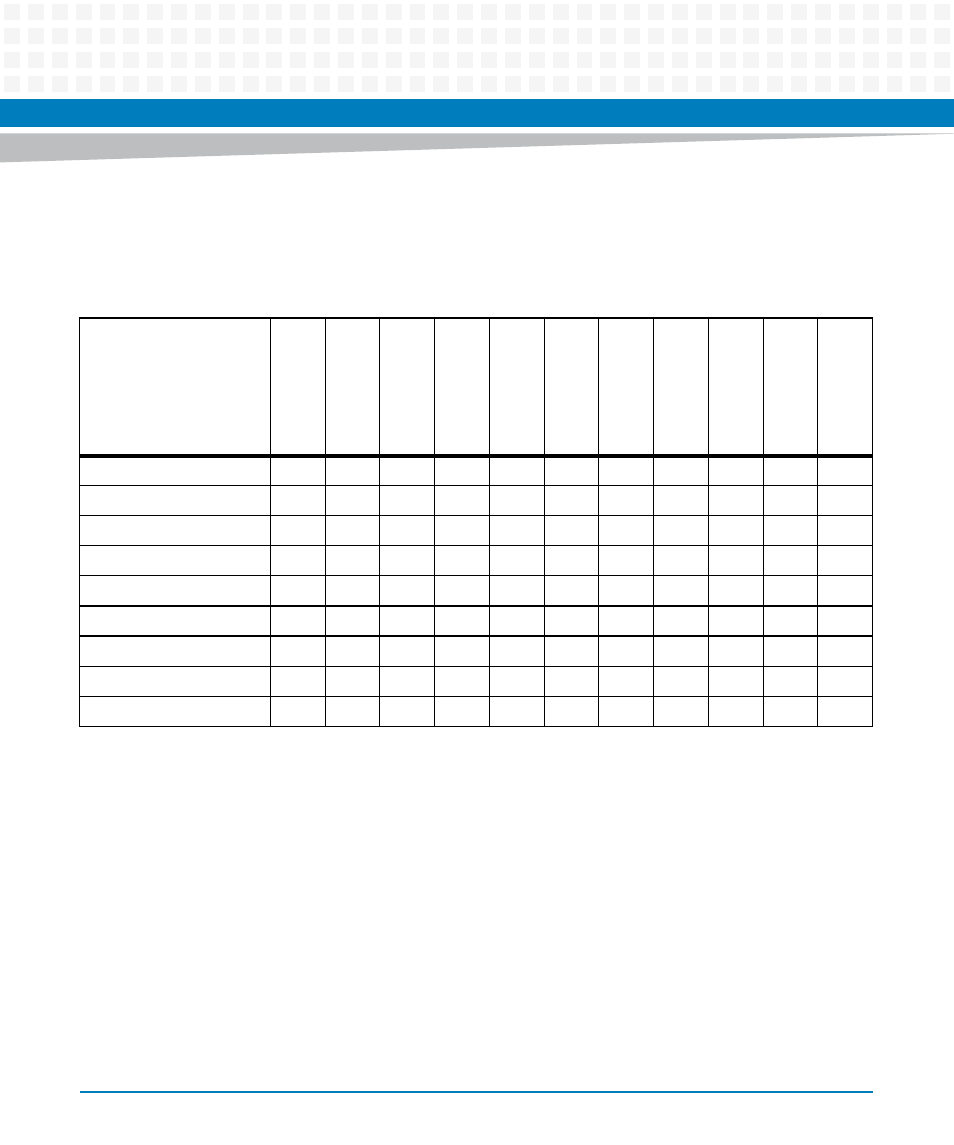

Table 4-7 Reset Signals

Reset Source

HR

ST_L

SR

ST_L

FIX_R

ST_L

BIX_R

ST_L

PHY_R

ST_L

QU

AD_PHY_R

ST_L

TEL

CO_R

ST_L

BIT

S_R

ST_L

MA

CPHY_R

ST_L

RTM_R

ST_L

DDR_R

ST_L

BOARD_PWR_OK

Yes

No

Yes

Yes

Yes

Yes

Yes

Yes

No

Yes

Yes

PAYLOAD_RST_L

Yes

No

Yes

Yes

Yes

Yes

Yes

Yes

No

Yes

No

FRONT_PANEL_RST_L

Yes

No

Yes

Yes

Yes

Yes

Yes

Yes

No

Yes

No

HRST_REQ_L

Yes

No

No

No

No

No

No

No

No

No

No

COP_HRESET_L

Yes

No

Yes

Yes

Yes

Yes

Yes

Yes

No

Yes

No

COP_SRESET_L

No

Yes

No

No

No

No

No

No

No

No

No

AMC_EN

No

No

No

No

No

No

No

No

Yes

No

No

AMC_PWR_GOOD

No

No

No

No

No

No

No

No

Yes

No

No

Software Control in FPGA

No

No

Yes

Yes

Yes

Yes

Yes

Yes

No

Yes

No