Cabletron Systems CSX1000 User Manual

Page 368

USER’S GUIDE

368 CyberSWITCH

V

ERIFYING

IP RIP I

NPUT

P

ROCESSING

ON

A

LAN I

NTERFACE

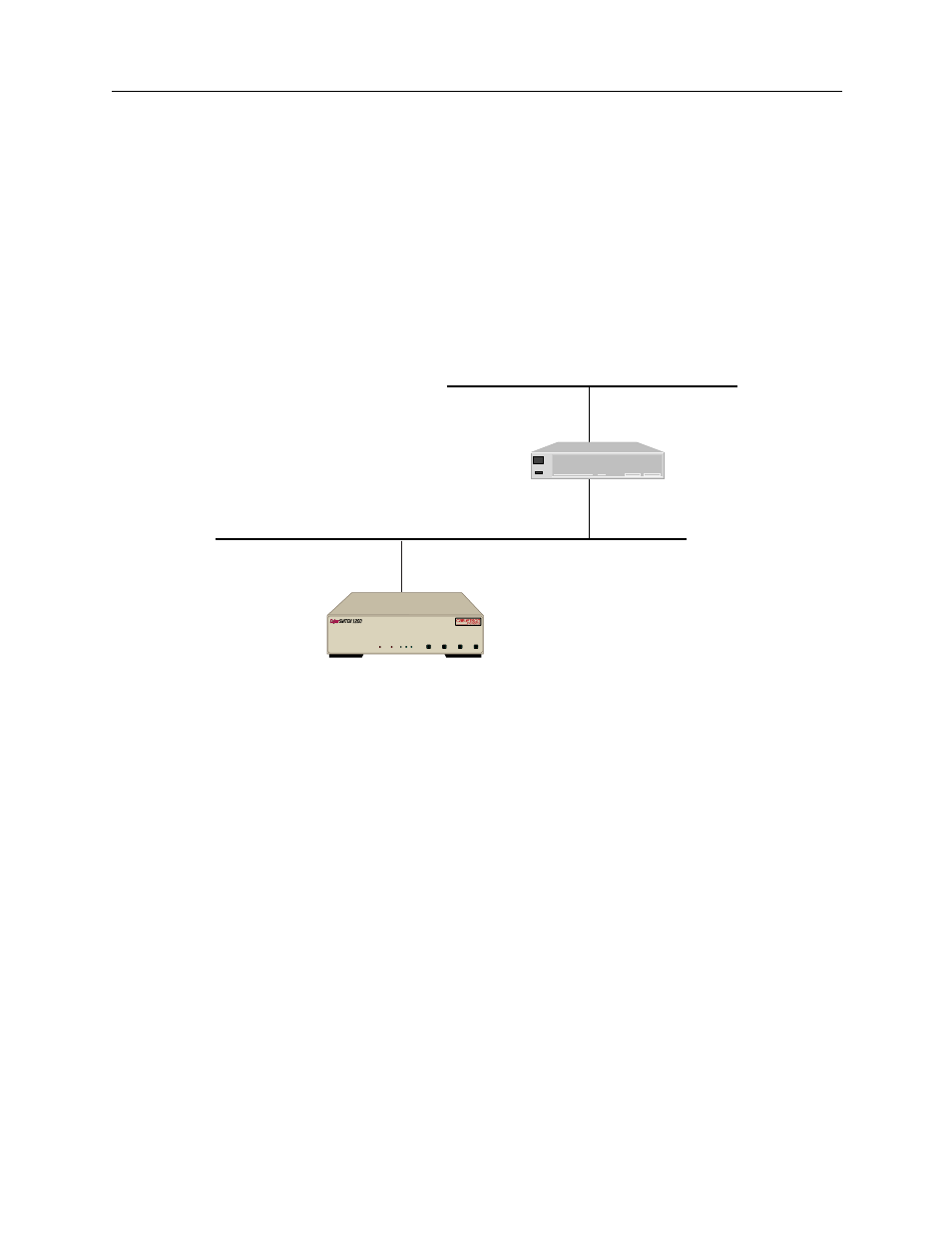

To verify that IP RIP Input Processing (routes learning) is properly operational on a LAN interface,

IP RIP processing must be successfully initialized. Also, a local IP router must be connected to the

local LAN port on the system and capable of propagating routes information via RIP.

Below is an example of a configuration used to verify IP RIP input processing on a LAN interface.

It uses IP addresses specified to the example. Substitute the IP addresses of your network when you

perform the verification steps. It also uses the

netstat

command. The

netstat

command

displays the IP routing table of the system. Substitute the equivalent command on your IP router.

To verify the operation of IP RIP input processing on a LAN interface:

1.

Determine if the CyberSWITCH has learned the route to 131.1.0.0 from Router 1. On the

administration console type:

ip route

If the following route entry is displayed among other route entries, the IP RIP input processing

is operational. The ‘P’ (Protocol) field should have ‘R’, which indicates that the entry was

learned via RIP.

Destination Subnet-Mask Next Hop Mtr T/P TTL IF AGE

131.1.0.0 255.255.0.0 128.1.1.16 1 R/R 999 n nnn

2.

If the route is NOT displayed, refer to

IP RIP Input Processing on a LAN Interface

in the Problem

Diagnosis chapter.

V

ERIFYING

IP RIP O

UTPUT

P

ROCESSING

ON

A

WAN I

NTERFACE

To verify that IP RIP Output Processing (routes advertisement) is properly operational on a WAN

interface, the IP RIP processing must be successfully initialized.

Below is an example of a configuration used to verify IP RIP output processing on a WAN interface.

It uses IP addresses specific to the example. Substitute the IP addresses of your network when you

LAN 131.1.0.0

Router 1

131.1.1.16

128.1.1.16

128.1.1.1

CSX1200

WORKGROUP REMOTE ACCESS SWITCH

LAN

10BASE-T

RX

TX

SERVICE

CH-2

D-CH

CH-1

SYNC

POWER

LINE

1

CH-2

D-CH

CH-1

SYNC

LINE

2

CH-2

D-CH

CH-1

SYNC

LINE

3

CH-2

D-CH

AGI

CH-1

SYNC

LINE

4