Maxq family user’s guide: maxq2000 supplement – Maxim Integrated MAXQ Family Users Guide: MAXQ2000 Supplement User Manual

Page 8

MAXQ Family User’s Guide:

MAXQ2000 Supplement

• 1-Wire Interface Master

• LCD Controller (up to 132 segments)

The lower 8 bits of all registers in modules 0 through 4 (as well as the AP module M8) are bit addressable.

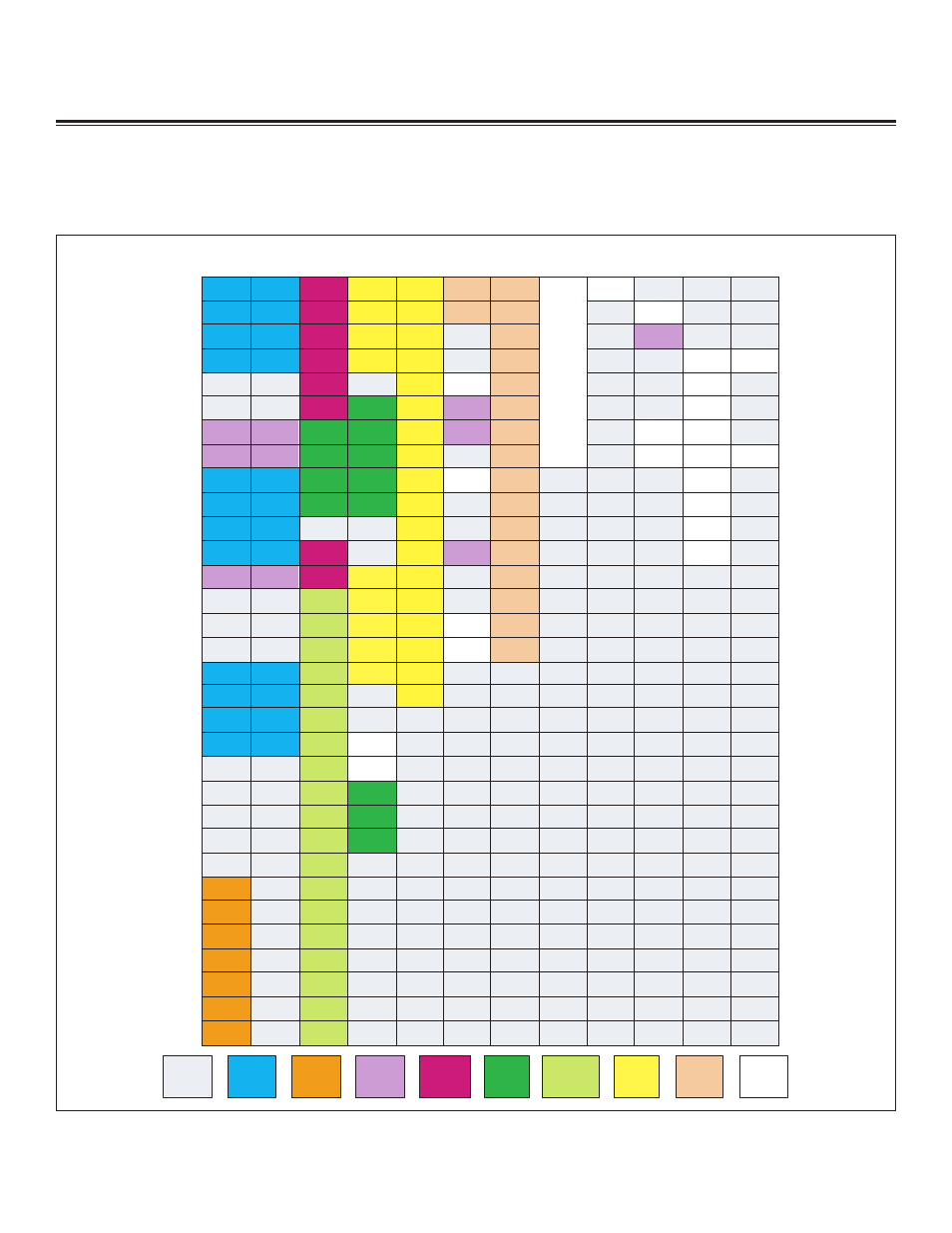

Figure 1. MAXQ2000 System and Peripheral Register Map

M0

M1

M2

M3

M4

M8

M9

M11

M12

M13

M14

M15

REAL-TIME

CLOCK

OWA

OWD

00h

01h

02h

03h

04h

05h

06h

07h

08h

09h

0Ah

0Bh

0Ch

0Dh

0Eh

0Fh

10h

11h

12h

13h

14h

15h

16h

17h

18h

19h

1Ah

1Bh

1Ch

1Dh

1Eh

1Fh

RESERVED

OR

OP CODE

PO0

PO4

PO1

PO5

PO2

PO6

PO3

PO7

PI0

PI4

PI1

PI5

PI2

PI6

PI3

PI7

PD0

PD4

PD1

PD5

PD2

PD6

PD3

PD7

RCNT

RTSS

RTSH

RTSL

RSSA

RASH

RASL

INTERRUPT

CONTROL

EIF0

EIF1

EIE0

EIE1

EIES0

EIES1

MA

MB

MC2

MC1

MC0

SERIAL

AND

SPI

LCD

CONTROLLER

TIMERS

ACC

ARRAY,

CONTROL

OTHER

FUNCTIONS

SCON0

SBUF0

SMD0

PR0

SPIB

SCON1

SBUF1

SMD1

PR1

SPICN

SPICF

SPICK

LCD15

LCD14

LCD13

LCD12

LCD11

LCD10

LCD9

LCD8

LCD7

LCD6

LCD5

LCD4

LCD3

LCD2

LCD1

LCD0

LCD16

LCFG

LCRA

T2CNA0

T2CNA1

T2H0

T2H1

T2RH0

T2RH1

T2CH0

T2CH1

T2CNA2

T2H2

T2RH2

T2CH2

T2CNB1

T2V1

T2R1

T2C1

T2CNB0

T2CNB2

T2V0

T2V2

T2R0

T2R2

T2C0

T2C2

T2CFG0

T2CFG1

T2CFG2

AP

APC

A[0]

A[1]

A[2]

A[3]

A[4]

A[5]

A[6]

A[7]

A[8]

A[9]

A[10]

A[11]

A[12]

A[13]

A[14]

A[15]

IP

SP

LC0

LC1

OFFS

DPC

GR

GRL

BP

GRS

GRH

GRXL

BP[offs]

DP0

DP1

PSF

CKCN

WDCN

SC

IC

IMR

IIR

IV

REGISTER MODULE

REGISTER INDEX

MC0R

PORT PINS

(GPIO)

HARDWARE

MULTIPLIER

MCNT

MC1R

PFX

Maxim Integrated

8