Maxq family user’s guide: maxq2000 supplement – Maxim Integrated MAXQ Family Users Guide: MAXQ2000 Supplement User Manual

Page 23

Bits 5 and 6: (SC.5 and SC.6) Reserved

Bit 7: (SC.7) Test Access (JTAG) Port Enable

0 = JTAG TAP functions are disabled and P4.0 through P4.3 can be used as general-purpose I/O pins.

1 = TAP special function pins P4.0 through P4.3 are enabled to act as JTAG inputs and outputs.

Register Name:

IIR

Register Description:

Interrupt Identification Register

Register Address:

AP[0Bh]

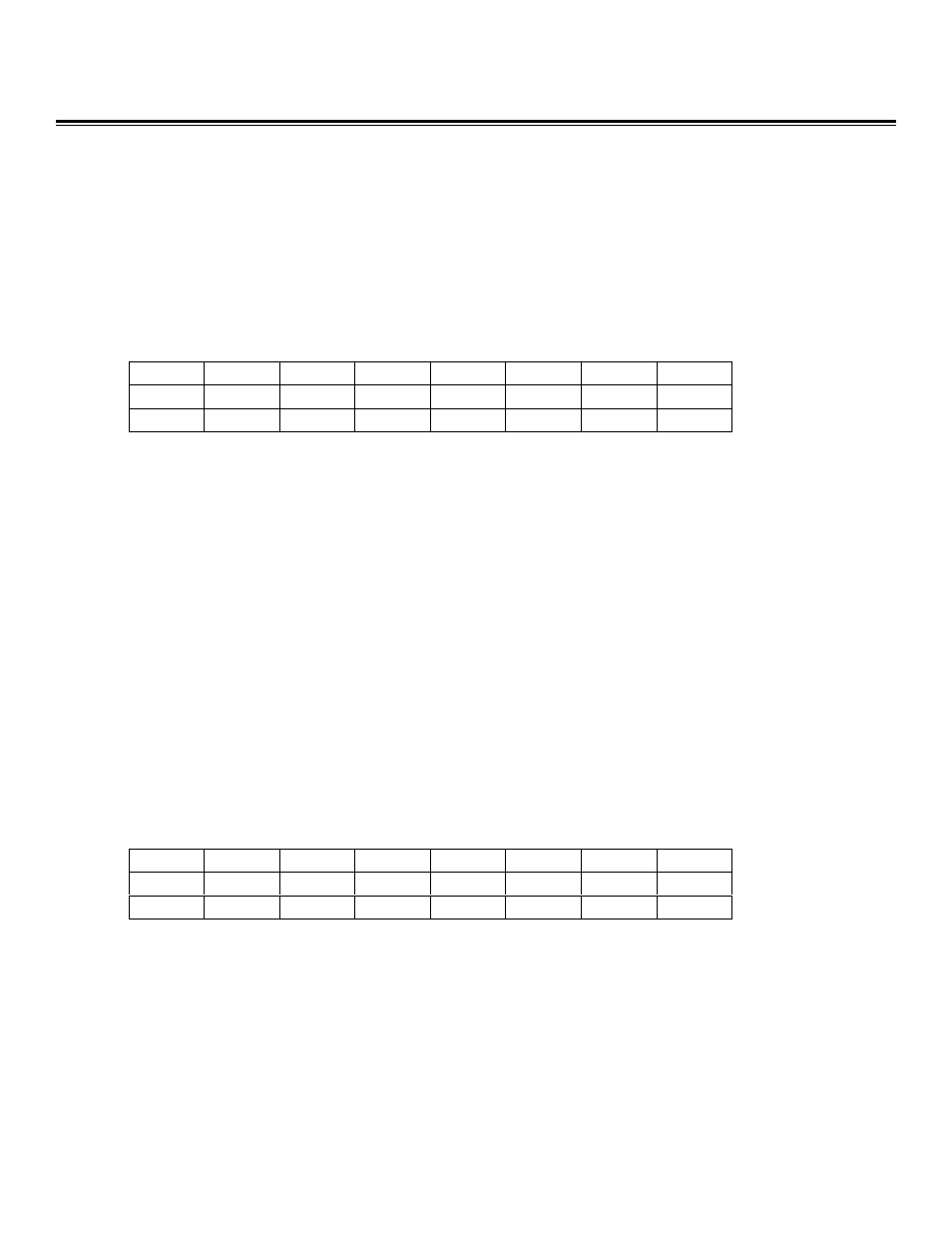

The first five bits in this register indicate interrupts pending in modules 0 through 4, one bit per module. The eighth bit, IIS, indicates a

pending system interrupt (from the watchdog timer or other system function). The interrupt pending flags will be set only for enabled

interrupt sources waiting for service. The interrupt pending flag will be cleared when the pending interrupt source(s) within that mod-

ule are disabled when the interrupt flag(s) are cleared by software.

Bit 0: (IIR.0) Interrupt Pending Flag for Module 0 (II0)

Bit 1: (IIR.1) Interrupt Pending Flag for Module 1 (II1)

Bit 2: (IIR.2) Interrupt Pending Flag for Module 2 (II2)

Bit 3: (IIR.3) Interrupt Pending Flag for Module 3 (II3)

Bit 4: (IIR.4) Interrupt Pending Flag for Module 4 (II4)

Bits 5 and 6: (IIR.5 and IIR.6) Reserved

Bit 7: (IIR.7) Interrupt Pending Flag for System Modules

Register Name:

CKCN

Register Description:

System Clock Control Register

Register Address:

AP[0Eh]

The CKCN register bit settings determine the system clock source and clock divider as described in the following table.

MAXQ Family User’s Guide:

MAXQ2000 Supplement

Bit #

7

6

5

4

3

2

1

0

Name

IIS

—

—

II4

II3

II2

II1

II0

Reset

0

0

0

0

0

0

0

0

Access

r

r

r

r

r

r

r

r

Bit #

7

6

5

4

3

2

1

0

Name

—

RGSL

RGMD

STOP

SWB

PMME

CD1

CD0

Reset

0

0

s

0

0

0

0

0

Access

r/w

r/w

r

r/w

r/w

r/w

special

special

Maxim Integrated

23